GVT71512ZB18

GVT71512ZB18 is 256K x 36 / 512K x 18 Flow Thru SRAM manufactured by Cypress.

- Part of the GVT71256ZB36 comparator family.

- Part of the GVT71256ZB36 comparator family.

( Data Sheet : .. )

1CY7C1357A

PRELIMINARY

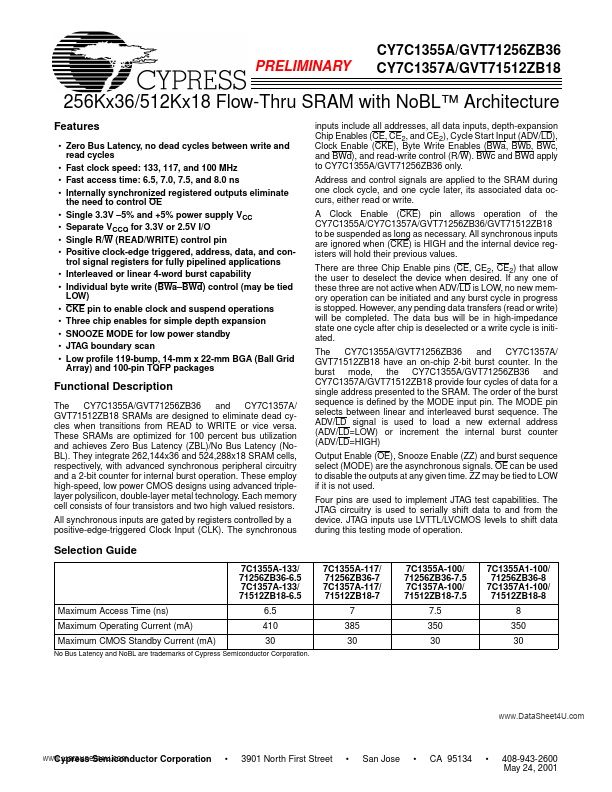

CY7C1355A/GVT71256ZB36 CY7C1357A/GVT71512ZB18

256Kx36/512Kx18 Flow-Thru SRAM with No BL™ Architecture

Features

- Zero Bus Latency, no dead cycles between write and read cycles

- Fast clock speed: 133, 117, and 100 MHz

- Fast access time: 6.5, 7.0, 7.5, and 8.0 ns

- Internally synchronized registered outputs eliminate the need to control OE

- Single 3.3V

- 5% and +5% power supply VCC

- Separate VCCQ for 3.3V or 2.5V I/O

- Single R/W (READ/WRITE) control pin

- Positive clock-edge triggered, address, data, and control signal registers for fully pipelined applications

- Interleaved or linear 4-word burst capability

- Individual byte write (BWa- BWd) control (may be tied LOW)

- CKE pin to enable clock and suspend operations

- Three chip enables for simple depth expansion

- SNOOZE MODE for low power standby

- JTAG boundary scan

- Low profile 119-bump, 14-mm x 22-mm BGA (Ball Grid Array) and 100-pin TQFP packages inputs include all addresses, all data inputs, depth-expansion Chip Enables (CE, CE2, and CE2), Cycle Start Input (ADV/LD), Clock Enable (CKE), Byte Write Enables (BWa, BWb, BWc, and BWd), and read-write control (R/W). BWc and BWd apply to CY7C1355A/GVT71256ZB36 only. Address and control signals are applied to the SRAM during one clock cycle, and one cycle later, its associated data occurs, either read or write. A Clock Enable (CKE) pin allows operation of the CY7C1355A/CY7C1357A/GVT71256ZB36/GVT71512ZB18 to be suspended as long as necessary. All synchronous inputs are ignored when (CKE) is HIGH and the internal device registers will hold their previous values. There are three Chip Enable pins (CE, CE2, CE2) that allow the user to deselect the device when desired. If any one of these three are not active when ADV/LD is LOW, no new memory operation can be initiated and any burst cycle in progress is stopped. However, any pending data transfers (read or write) will be pleted. The data bus will be in...