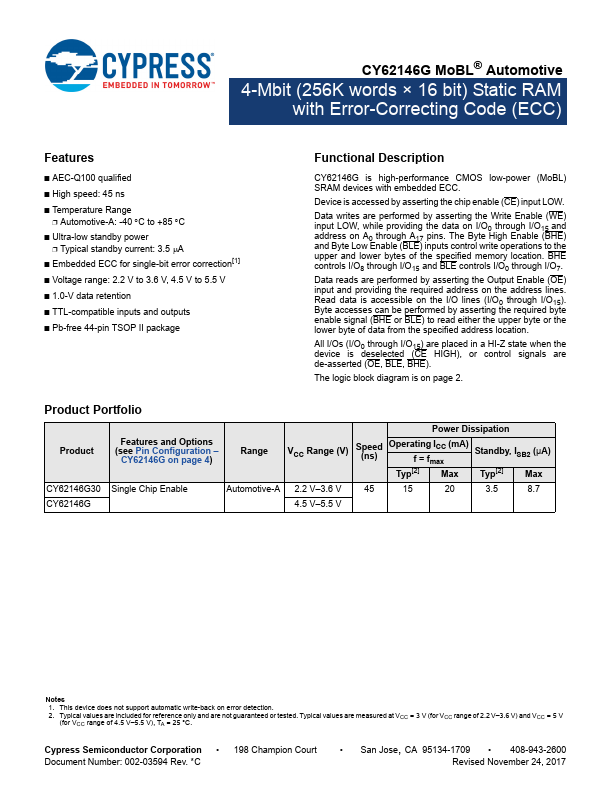

| Part | CY62146G-MoBL |

|---|---|

| Description | 4-Mbit (256K words x 16 bit) Static RAM |

| Manufacturer | Cypress |

| Size | 486.82 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| CY62146CV30 | Cypress | 256K x 16 Static RAM |

| CY62146CV18 | Cypress | 256K x 16 Static RAM |

| CY62146E | Cypress | 4-Mbit (256K x 16) Static RAM |

| CY62146ESL | Cypress | 4-Mbit (256K x 16) Static RAM |

| CY62146EV30 | Cypress | 4-Mbit (256K x 16) Static RAM |