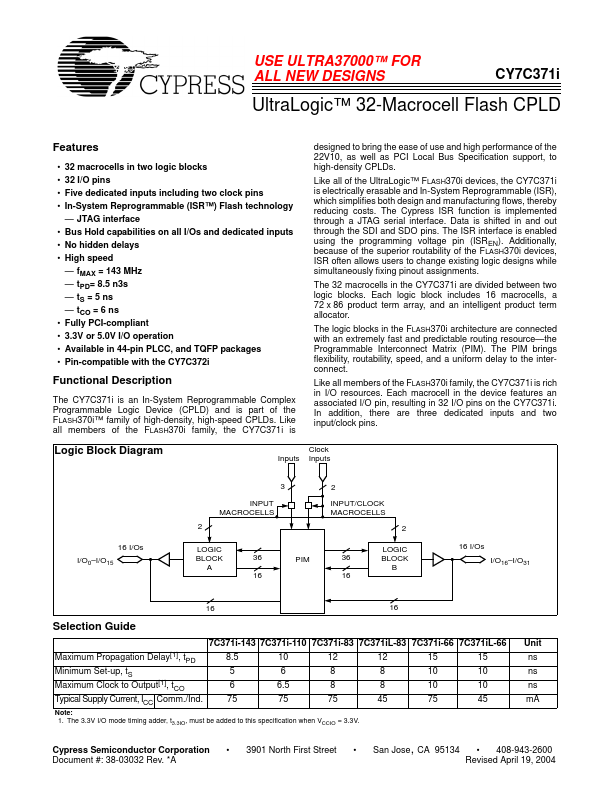

CY7C371I Description

The CY7C371i is an In-System Reprogrammable plex Programmable Logic Device (CPLD) and is part of the FLASH370i™ family of high-density, high-speed CPLDs. The 3.3V I/O mode timing adder, t3.3IO, must be added to this specification when VCCIO = 3.3V. Cypress Semiconductor Corporation Document.

CY7C371I Key Features

- 32 macrocells in two logic blocks 32 I/O pins Five dedicated inputs including two clock pins In-System Reprogrammable (I

- JTAG interface Bus Hold capabilities on all I/Os and dedicated inputs No hidden delays High speed

- fMAX = 143 MHz

- tPD= 8.5 n3s

- tS = 5 ns

- 3901 North First Street

- San Jose, CA 95134

- 408-943-2600 Revised April 19, 2004