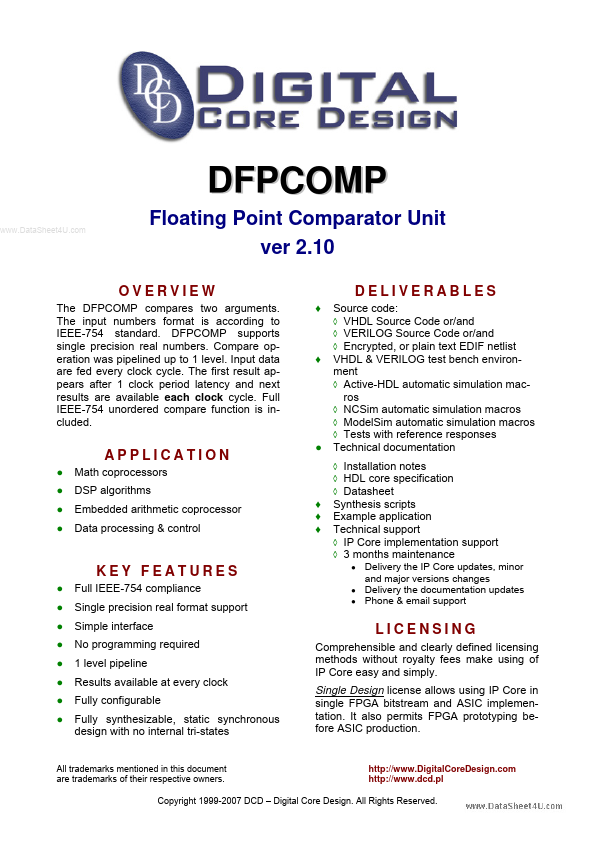

DFPCOMP

OVERVIEW

DELIVERABLES

- Source code: VHDL Source Code or/and VERILOG Source Code or/and Encrypted, or plain text EDIF netlist VHDL & VERILOG test bench environment ◊ Active-HDL automatic simulation macros ◊ NCSim automatic simulation macros ◊ Model Sim automatic simulation macros ◊ Tests with reference responses Technical documentation

◊ ◊ ◊

The DFPP pares two arguments. The input numbers format is according to IEEE-754 standard. DFPP supports single precision real numbers. pare operation was pipelined up to 1 level. Input data are fed every clock cycle. The first result appears after 1 clock period latency and next results are available each clock cycle. Full IEEE-754 unordered pare function is included.

- APPLICATION

- -

- - Math coprocessors DSP algorithms Embedded arithmetic coprocessor Data processing & control

- -

- -

Installation notes HDL core specification Datasheet Synthesis scripts Example application Technical support ◊ IP Core implementation support ◊ 3 months...