M13D64322A-4.5BG2S

M13D64322A-4.5BG2S is 512K x 32 Bit x 4 Banks LPDDR SDRAM manufactured by Elite Semiconductor Microelectronics Technology.

- Part of the M13D64322A comparator family.

- Part of the M13D64322A comparator family.

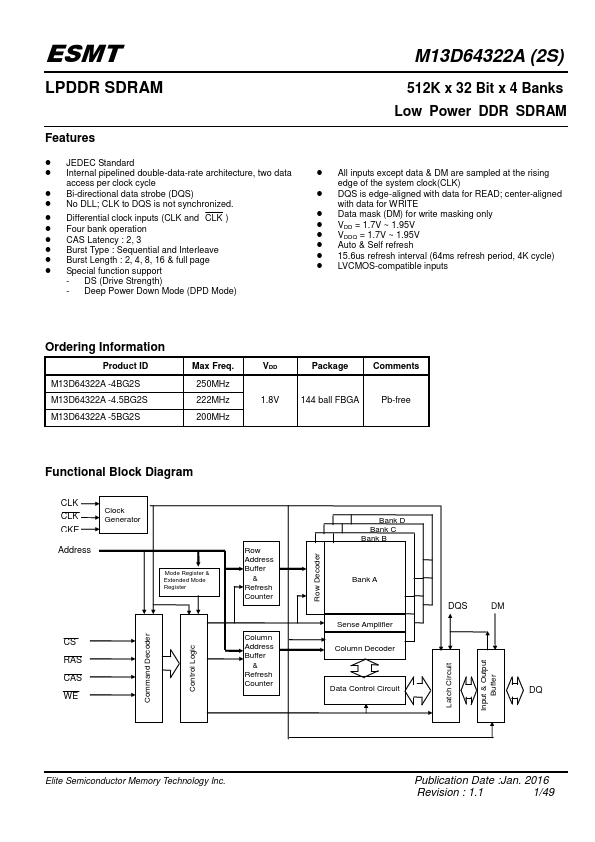

Features

JEDEC Standard Internal pipelined double-data-rate architecture, two data access per clock cycle Bi-directional data strobe (DQS) No DLL; CLK to DQS is not synchronized. Differential clock inputs (CLK and CLK ) Four bank operation CAS Latency : 2, 3 Burst Type : Sequential and Interleave Burst Length : 2, 4, 8, 16 & full page Special function support

- DS (Drive Strength)

- Deep Power Down Mode (DPD Mode)

M13D64322A (2S)

512K x 32 Bit x 4 Banks Low Power DDR SDRAM

All inputs except data & DM are sampled at the rising edge of the system clock(CLK) DQS is edge-aligned with data for READ; center-aligned with data for WRITE Data mask (DM) for write masking only VDD = 1.7V ~ 1.95V VDDQ = 1.7V ~ 1.95V Auto & Self refresh 15.6us refresh interval (64ms refresh period, 4K cycle) LVCMOS-patible inputs

Ordering Information

Product ID M13D64322A -4BG2S M13D64322A -4.5BG2S M13D64322A -5BG2S

Max Freq. 250MHz 222MHz 200MHz

Package ments

1.8V 144 ball FBGA Pb-free

Functional Block Diagram

CLK CLK CKE

Clock Generator

Address

Mode Register & Extended Mode Register

Row Address Buffer

& Refresh Counter

CS RAS CAS WE

Column Address Buffer

& Refresh Counter

Bank D Bank C Bank B

Bank A

Sense Amplifier Column Decoder

Data Control Circuit

DQ mand Decoder Control Logic Row Decoder

Latch Circuit Input & Output

Buffer

Elite Semiconductor Memory Technology Inc.

Publication Date :Jan. 2016

Revision : 1.1

1/49

ESMT

M13D64322A (2S)

BALL CONFIGURATION (TOP VIEW)

(BGA144, 12mm X12mm X1.4m Body, 0.8mm Ball...