M13L32321A

M13L32321A is Double Data Rate SDRAM manufactured by Elite Semiconductor Microelectronics Technology.

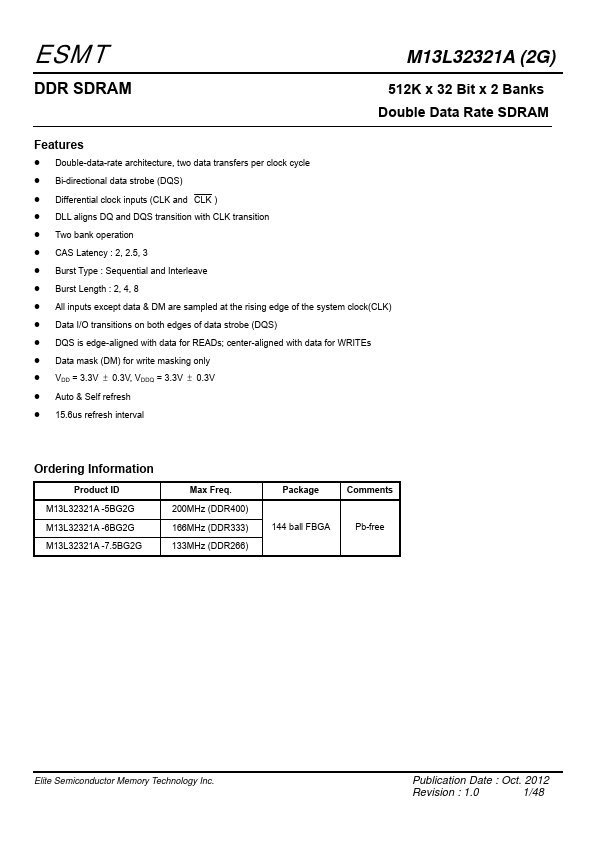

Features z Double-data-rate architecture, two data transfers per clock cycle z Bi-directional data strobe (DQS) z Differential clock inputs (CLK and CLK ) z DLL aligns DQ and DQS transition with CLK transition z Two bank operation z CAS Latency : 2, 2.5, 3 z Burst Type : Sequential and Interleave z Burst Length : 2, 4, 8 z All inputs except data & DM are sampled at the rising edge of the system clock(CLK) z Data I/O transitions on both edges of data strobe (DQS) z DQS is edge-aligned with data for READs; center-aligned with data for WRITEs z Data mask (DM) for write masking only z VDD = 3.3V ± 0.3V, VDDQ = 3.3V ± 0.3V z Auto & Self refresh z 15.6us refresh interval

Ordering Information

Product ID M13L32321A -5BG2G M13L32321A -6BG2G M13L32321A -7.5BG2G

Max Freq. 200MHz (DDR400) 166MHz (DDR333) 133MHz (DDR266)

Package ments

144 ball FBGA

Pb-free

Elite Semiconductor Memory Technology...