M52D256328A

M52D256328A is 2M x 32 Bit x 4 Banks Mobile SDRAM manufactured by Elite Semiconductor Microelectronics Technology.

FEATURES

- 1.8V power supply

- LVCMOS patible with multiplexed address

- Four banks operation

- MRS cycle with address key programs

- CAS Latency (3)

- Burst Length (1, 2, 4, 8 & full page)

- Burst Type (Sequential & Interleave)

- EMRS cycle with address

- All inputs are sampled at the positive going edge of the system clock

- Special function support

- PASR (Partial Array Self Refresh)

- TCSR (Temperature pensated Self Refresh)

- DS (Driver Strength)

- DQM for masking

- Auto & self refresh

- 64ms refresh period (4K cycle)

M52D256328A (2F)

2M x 32 Bit x 4 Banks

Mobile Synchronous DRAM

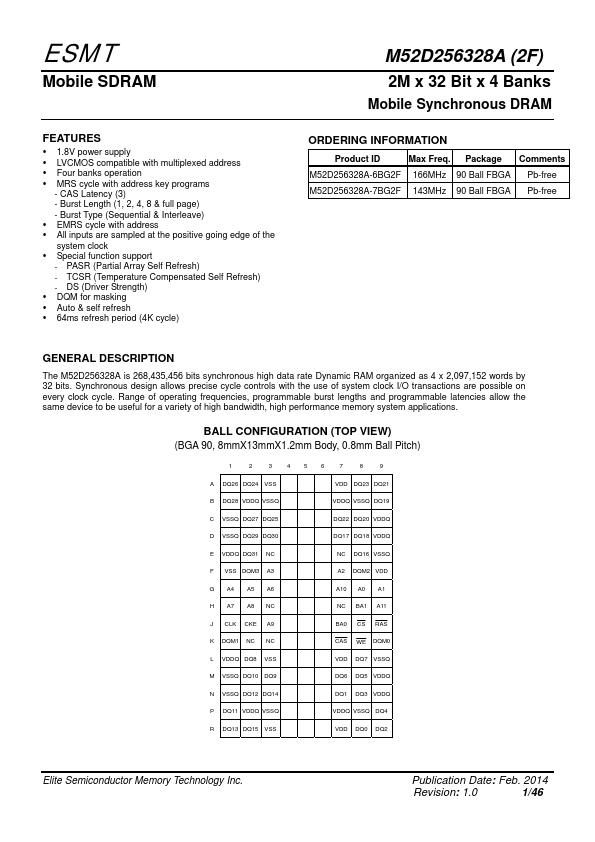

ORDERING INFORMATION

Product ID

Max Freq. Package ments

M52D256328A-6BG2F 166MHz 90 Ball FBGA Pb-free

M52D256328A-7BG2F 143MHz 90 Ball FBGA Pb-free

GENERAL DESCRIPTION

The M52D256328A is 268,435,456 bits synchronous high data rate Dynamic RAM organized as 4 x 2,097,152 words by 32 bits. Synchronous design allows precise cycle controls with the use of...