M24L28256DA

M24L28256DA is 2-Mbit (256K x 8) Pseudo Static RAM manufactured by Elite Semiconductor Memory Technology.

ESMT

PSRAM

Features

- Advanced low-power architecture

- High speed: 55 ns, 70 ns

- Wide voltage range: 2.7V to 3.3V

- Typical active current: 1 mA @ f = 1 MHz

- Low standby power

- Automatic power-down when deselected

..

M24L28256DA 2-Mbit (256K x 8) Pseudo Static RAM

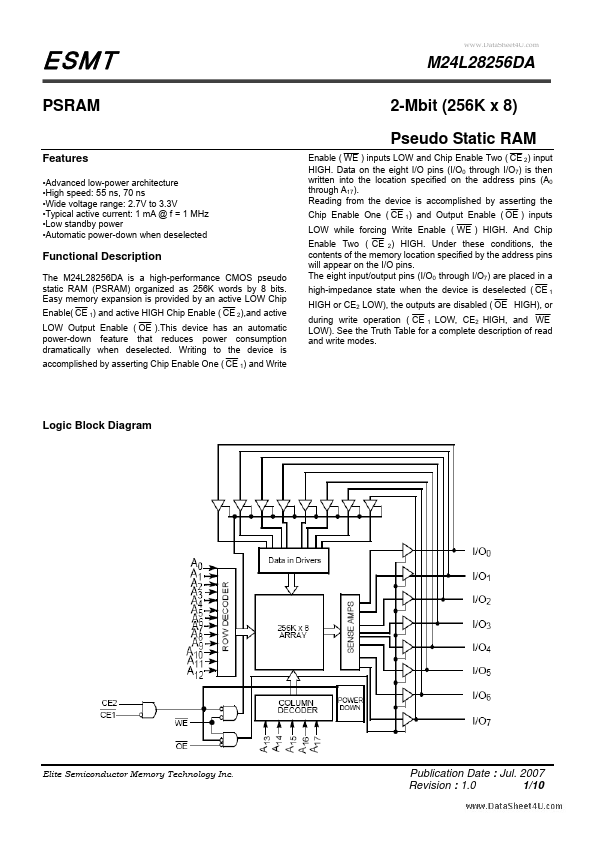

Enable ( WE ) inputs LOW and Chip Enable Two ( CE 2) input HIGH. Data on the eight I/O pins (I/O0 through I/O7) is then written into the location specified on the address pins (A0 through A17). Reading from the device is acplished by asserting the Chip Enable One ( CE 1) and Output Enable ( OE ) inputs LOW while forcing Write Enable ( WE ) HIGH. And Chip Enable Two ( CE 2) HIGH. Under these conditions, the...