M24L416256DA Description

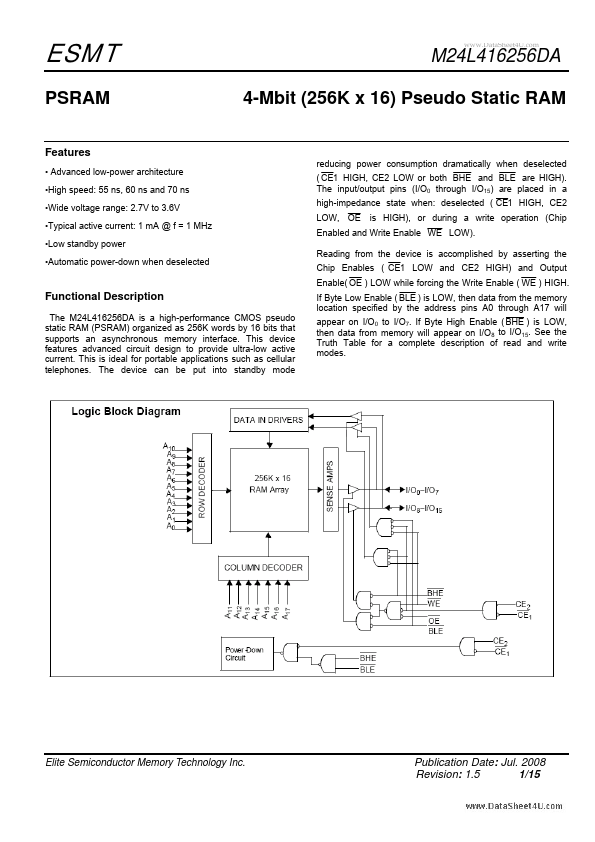

Functional Description The M24L416256DA is a high-performance CMOS pseudo static RAM (PSRAM) organized as 256K words by 16 bits that supports an asynchronous memory interface.

M24L416256DA Key Features

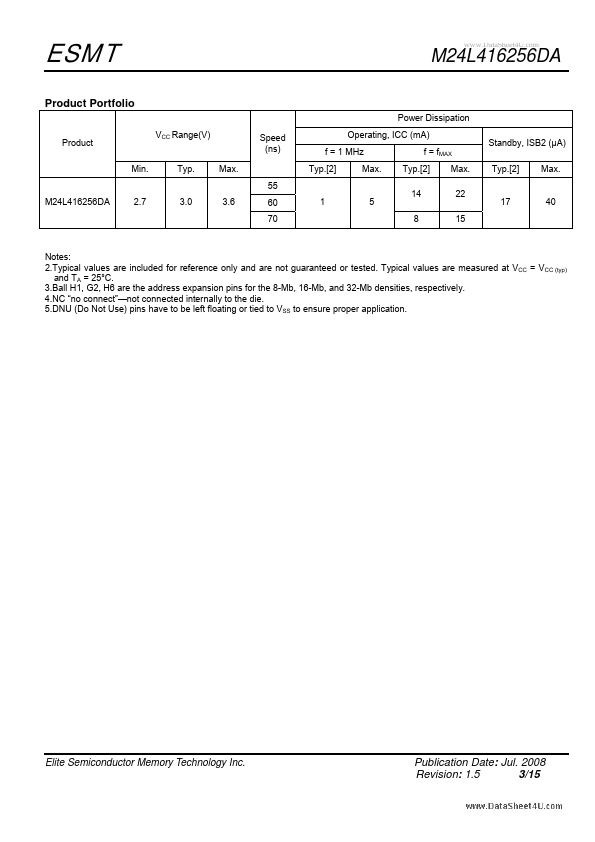

- Advanced low-power architecture -High speed: 55 ns, 60 ns and 70 ns -Wide voltage range: 2.7V to 3.6V -Typical active cu