EDD5116ADTA

EDD5116ADTA is 512M bits DDR SDRAM manufactured by Elpida Memory.

- Part of the EDD5108ADTA comparator family.

- Part of the EDD5108ADTA comparator family.

Description

The EDD5104AD, the EDD5108AD and the EDD5116AD are 512M bits Double Data Rate (DDR) SDRAM. Read and write operations are performed at the cross points of the CK and the /CK. This highspeed data transfer is realized by the 2 bits prefetchpipelined architecture. Data strobe (DQS) both for read and write are available for high speed and reliable data bus design. By setting extended mode register, the on-chip Delay Locked Loop (DLL) can be set enable or disable. It is packaged in standard 66-pin plastic TSOP (II).

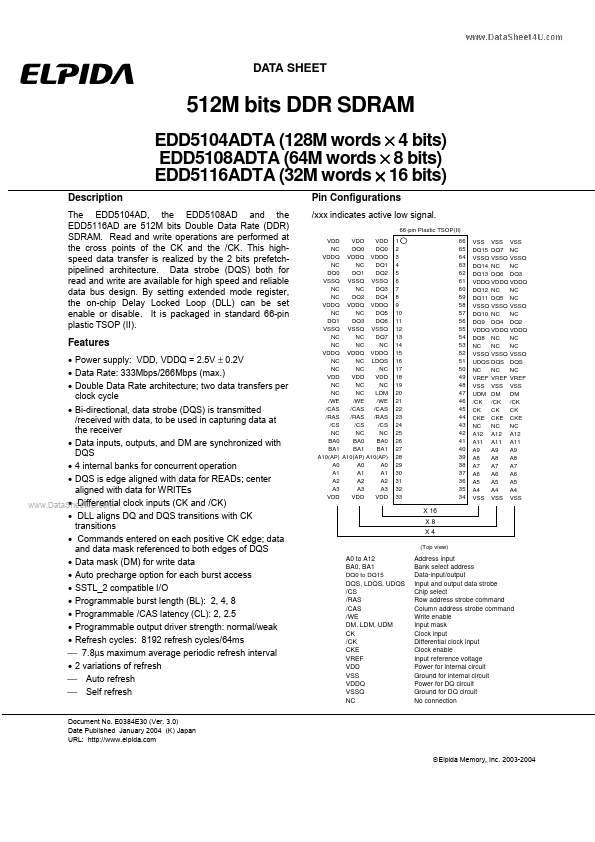

Pin Configurations

/xxx indicates active low signal.

66-pin Plastic TSOP(II) VDD VDD VDD NC DQ0 DQ0 VDDQ VDDQ VDDQ NC NC DQ1 DQ0 DQ1 DQ2 VSSQ VSSQ VSSQ NC NC DQ3 NC DQ2 DQ4 VDDQ VDDQ VDDQ NC NC DQ5 DQ1 DQ3 DQ6 VSSQ VSSQ VSSQ NC NC DQ7 NC NC NC VDDQ VDDQ VDDQ NC NC LDQS NC NC NC VDD VDD VDD NC NC NC NC NC LDM /WE /WE /WE /CAS /CAS /CAS /RAS /RAS /RAS /CS /CS /CS NC NC NC BA0 BA0 BA0 BA1 BA1 BA1 A10(AP) A10(AP) A10(AP) A0 A0 A0 A1 A1 A1 A2 A2 A2 A3 A3 A3 VDD VDD VDD 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 VSS VSS VSS DQ15 DQ7 NC VSSQ VSSQ VSSQ DQ14 NC NC DQ13 DQ6 DQ3 VDDQ VDDQ VDDQ DQ12 NC NC DQ11 DQ5 NC VSSQ VSSQ VSSQ DQ10 NC NC DQ9 DQ4 DQ2 VDDQ VDDQ VDDQ DQ8 NC NC NC NC NC VSSQ VSSQ VSSQ UDQS DQS DQS NC NC NC VREF VREF VREF VSS VSS VSS UDM DM DM /CK /CK /CK CK CK CK CKE CKE CKE NC NC NC A12 A12 A12 A11 A11 A11 A9 A9 A9 A8 A8 A8 A7 A7 A7 A6 A6 A6 A5 A5 A5 A4 A4 A4 VSS VSS VSS

Features

- Power supply: VDD, VDDQ = 2.5V ± 0.2V

- Data Rate: 333Mbps/266Mbps (max.)

- Double Data Rate architecture; two data transfers per clock cycle

- Bi-directional, data strobe (DQS) is transmitted /received with data, to be used in capturing data at the receiver

- Data inputs, outputs, and DM are synchronized with DQS

- 4 internal banks for concurrent operation

- DQS is edge aligned with data for READs; center aligned...