EDD5116AGTA

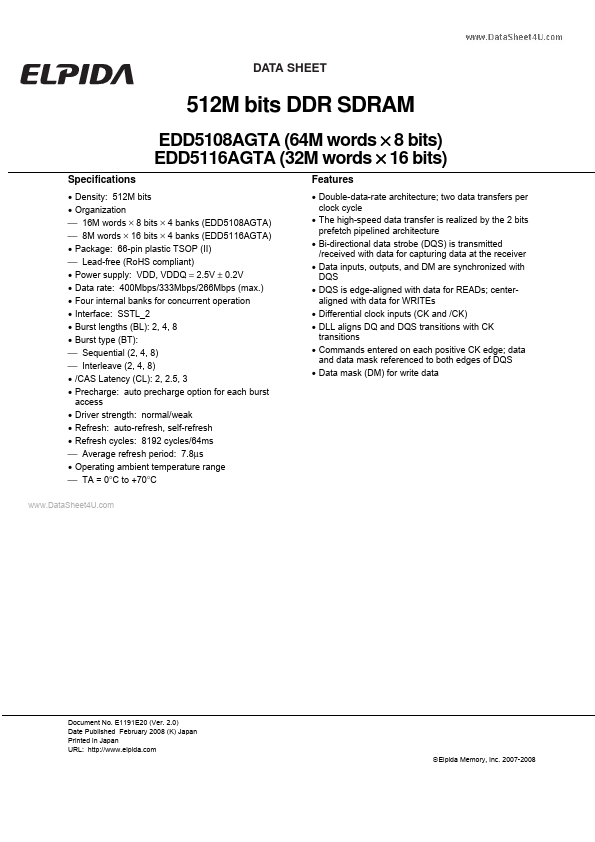

EDD5116AGTA is 512M bits DDR SDRAM manufactured by Elpida Memory.

- Part of the EDD5108AGTA comparator family.

- Part of the EDD5108AGTA comparator family.

Features

- Double-data-rate architecture; two data transfers per clock cycle

- The high-speed data transfer is realized by the 2 bits prefetch pipelined architecture

- Bi-directional data strobe (DQS) is transmitted /received with data for capturing data at the receiver

- Data inputs, outputs, and DM are synchronized with DQS

- DQS is edge-aligned with data for READs; centeraligned with data for WRITEs

- Differential clock inputs (CK and /CK)

- DLL aligns DQ and DQS transitions with CK transitions

- mands entered on each positive CK edge; data and data mask referenced to both edges of DQS

- Data mask (DM) for write data

Document No. E1191E20 (Ver. 2.0) Date Published February 2008 (K) Japan Printed in Japan URL: http://.elpida. ©Elpida Memory, Inc. 2007-2008

EDD5108AGTA, EDD5116AGTA

Ordering Information

Part number EDD5108AGTA-5B-E EDD5108AGTA-5C-E EDD5108AGTA-6B-E EDD5108AGTA-7A-E EDD5108AGTA-7B-E EDD5116AGTA-5B-E EDD5116AGTA-5C-E EDD5116AGTA-6B-E EDD5116AGTA-7A-E EDD5116AGTA-7B-E Mask version G Organization (words × bits) 64M × 8 Internal banks 4 Data rate Mbps (max.) 400 333 266 32M × 16 400 333 266 JEDEC speed bin (CL-t RCD-t RP) DDR400B (3-3-3) DDR400C (3-4-4) DDR333B (2.5-3-3) DDR266A (2-3-3) DDR266B (2.5-3-3) DDR400B (3-3-3) DDR400C (3-4-4) DDR333B (2.5-3-3) DDR266A (2-3-3) DDR266B (2.5-3-3) Package 66-pin Plastic TSOP (II)

Part Number

E D D 51 08 A G TA

- 5B

- E

Elpida Memory Environment Code E: Lead Free (Ro HS pliant) Type D: Monolithic Device Product Family D: DDR SDRAM Density / Bank 51: 512M / 4-bank Organization 08: x8 16: x16 Power Supply, Interface A: 2.5V, SSTL_2 Speed 5B: DDR400B (3-3-3) 5C: DDR400C (3-4-4) 6B: DDR333B (2.5-3-3) 7A: DDR266A (2-3-3) 7B: DDR266B (2.5-3-3) Package TA: TSOP (II) Die Rev.

Speed Grade patibility

Operating Frequencies Speed bin .. DDR400B DDR400C DDR333B DDR266A DDR266B CL2 133MHz 133MHz 133MHz 133MHz 100MHz CL2.5 166MHz 166MHz 166MHz 133MHz 133MHz CL3 200MHz 200MHz 166MHz 133MHz 133MHz

Data Sheet E1191E20 (Ver....