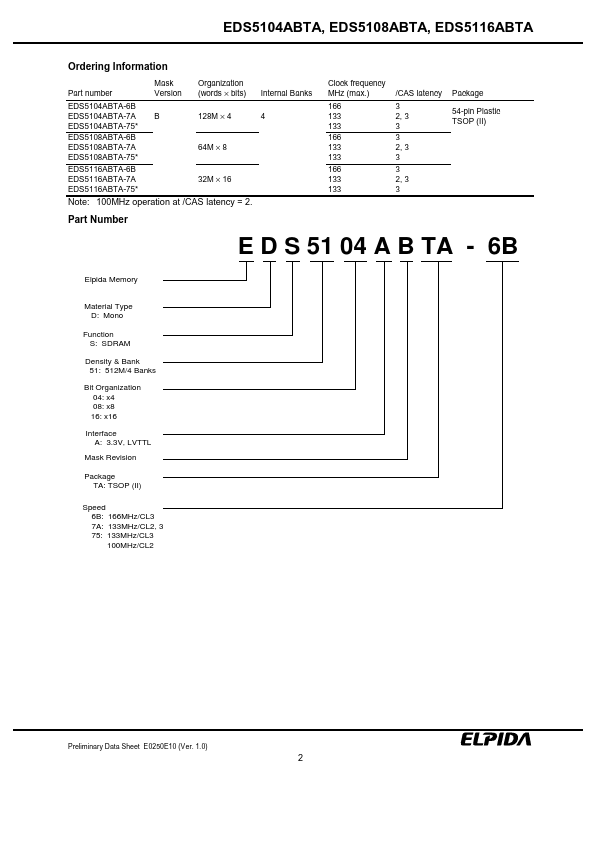

Datasheet Summary

PRELIMINARY DATA SHEET

512M bits SDRAM

EDS5104ABTA (128M words × 4 bits) EDS5108ABTA (64M words × 8 bits) EDS5116ABTA (32M words × 16 bits)

Description

The EDS5104AB is a 512M bits SDRAM organized as 33,554,432 words × 4 bits × 4 banks. The EDS5108AB is a 512M bits SDRAM organized as 16,777,216 words × 8 bits × 4 banks. The EDS5116AB is a 512M bits SDRAM organized as 8,388,608 words × 16 bits × 4 banks. All inputs and outputs are referred to the rising edge of the clock input. It is packaged in standard 54pin plastic TSOP (II).

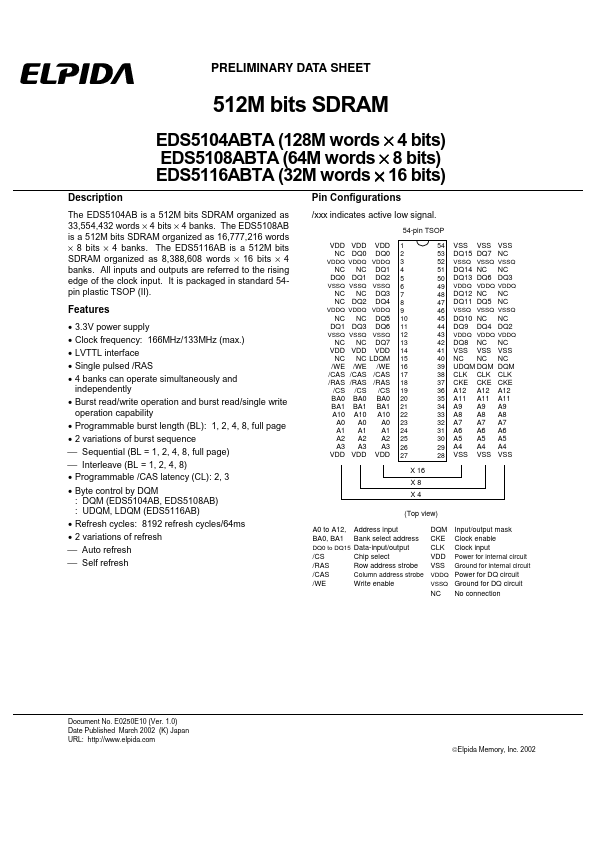

Pin Configurations

/xxx indicates active low signal.

54-pin TSOP VDD VDD NC DQ0 NC NC DQ0 DQ1 NC NC NC DQ2 NC NC DQ1 DQ3 NC VDD NC /WE /CAS /RAS /CS BA0 BA1 A10...