XRK32309

XRK32309 is LOW-COST 3.3V ZERO DELAY BUFFER manufactured by Exar.

DESCRIPTION

FUNCTIONAL DESCRIPTION

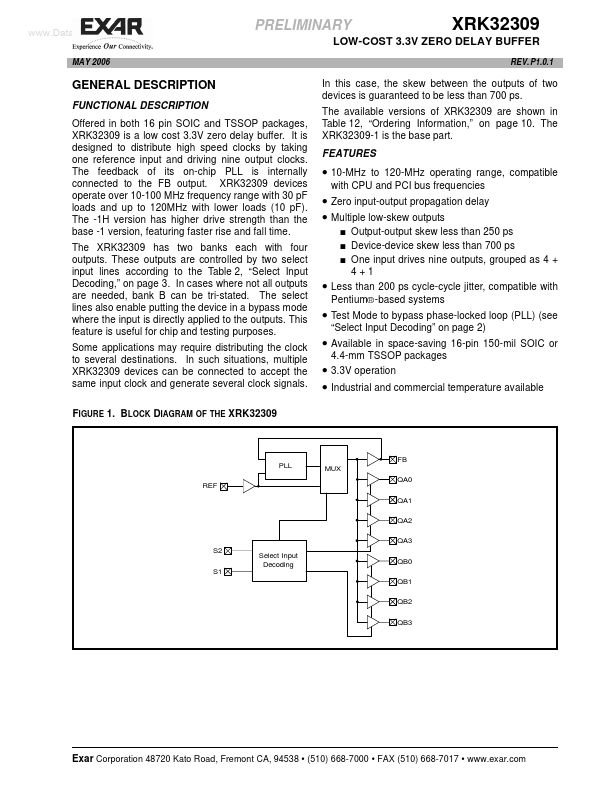

Offered in both 16 pin SOIC and TSSOP packages, XRK32309 is a low cost 3.3V zero delay buffer. It is designed to distribute high speed clocks by taking one reference input and driving nine output clocks. The feedback of its on-chip PLL is internally connected to the FB output. XRK32309 devices operate over 10-100 MHz frequency range with 30 p F loads and up to 120MHz with lower loads (10 p F). The -1H version has higher drive strength than the base -1 version, featuring faster rise and fall time. The XRK32309 has two banks each with four outputs. These outputs are controlled by two select input lines according to the Table 2, “Select Input Decoding,” on page 3. In cases where not all outputs are needed, bank B can be tri-stated. The select lines also enable putting the device in a bypass mode where the input is directly applied to the outputs. This feature is useful for chip and testing purposes. Some applications may require distributing the clock to several destinations. In such situations, multiple XRK32309 devices can be connected to accept the same input clock and generate several clock signals. FIGURE 1. BLOCK DIAGRAM OF THE XRK32309

In this case, the skew between the outputs of two devices is guaranteed to be less than 700 ps. The available versions of XRK32309 are shown in Table 12, “Ordering Information,” on page 10. The XRK32309-1 is the base part. FEATURES

- 10-MHz to 120-MHz operating range, patible with CPU and PCI bus frequencies

- Zero input-output propagation delay

- Multiple low-skew outputs

- -

- Output-output skew less than 250 ps Device-device skew less than 700 ps One input drives nine outputs, grouped as 4 + 4+1

- Less than 200 ps cycle-cycle jitter, patible with

- Test Mode to bypass phase-locked loop (PLL) (see

“Select Input Decoding” on page 2) Pentium®-based systems

- Available in space-saving 16-pin 150-mil SOIC or

4.4-mm TSSOP packages

- 3.3V operation

- Industrial and mercial temperature...