XRK39351

XRK39351 is 9-OUTPUT PLL CLOCK DRIVER manufactured by Exar.

FEATURES

GENERAL DESCRIPTION

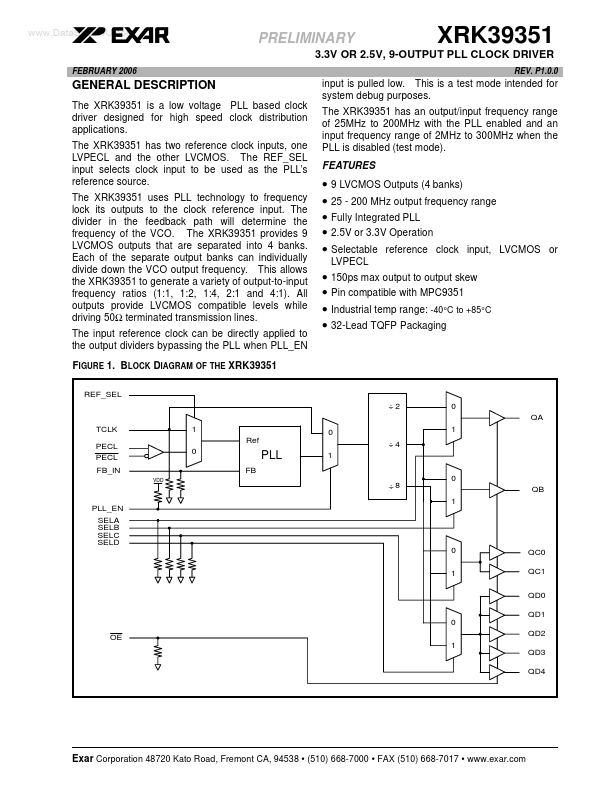

The XRK39351 is a low voltage PLL based clock driver designed for high speed clock distribution applications. The XRK39351 has two reference clock inputs, one LVPECL and the other LVCMOS. The REF_SEL input selects clock input to be used as the PLL’s reference source. The XRK39351 uses PLL technology to frequency lock its outputs to the clock reference input. The divider in the feedback path will determine the frequency of the VCO. The XRK39351 provides 9 LVCMOS outputs that are separated into 4 banks. Each of the separate output banks can individually divide down the VCO output frequency. This allows the XRK39351 to generate a variety of output-to-input frequency ratios (1:1, 1:2, 1:4, 2:1 and 4:1). All outputs provide LVCMOS patible levels while driving 50Ω terminated transmission lines. The input reference clock can be directly applied to the output dividers bypassing the PLL when PLL_EN FIGURE 1. BLOCK DIAGRAM OF THE XRK39351

REF_SEL

- -

- -

- -

- -

- 9 LVCMOS Outputs (4 banks) 25

- 200 MHz output frequency range Fully Integrated PLL 2.5V or 3.3V Operation Selectable reference clock input, LVCMOS or LVPECL 150ps max output to output skew Pin patible with MPC9351 Industrial temp range: -40°C to +85°C 32-Lead TQFP Packaging

÷2 TCLK PECL PECL FB_IN

0 QA 1

1 Ref 0 FB

0 ÷4

1 0 QB 1

÷8

PLL_EN SELA SELB SELC SELD

0 1

QC0 QC1 QD0

0 OE 1

QD1 QD2 QD3 QD4

Exar Corporation 48720 Kato Road, Fremont CA, 94538

- (510) 668-7000

- FAX (510) 668-7017

- .exar.

XRK39351 PRELIMINARY 3.3V OR 2.5V, 9-OUTPUT PLL CLOCK DRIVER

PRODUCT ORDERING INFORMATION

PRODUCT NUMBER XRK39351IQ PACKAGE TYPE 32-Lead TQFP xr

OPERATING TEMPERATURE RANGE -40°C to +85°C

REV. P1.0.0

FIGURE 2. PIN OUT OF THE XRK39351

REF_SEL

PLL_EN

VCCQB

TCLK

32 AVCC FB_IN SELA SELB SELC SELD AGND PECL 1 2 3 4 5 6 7 8...