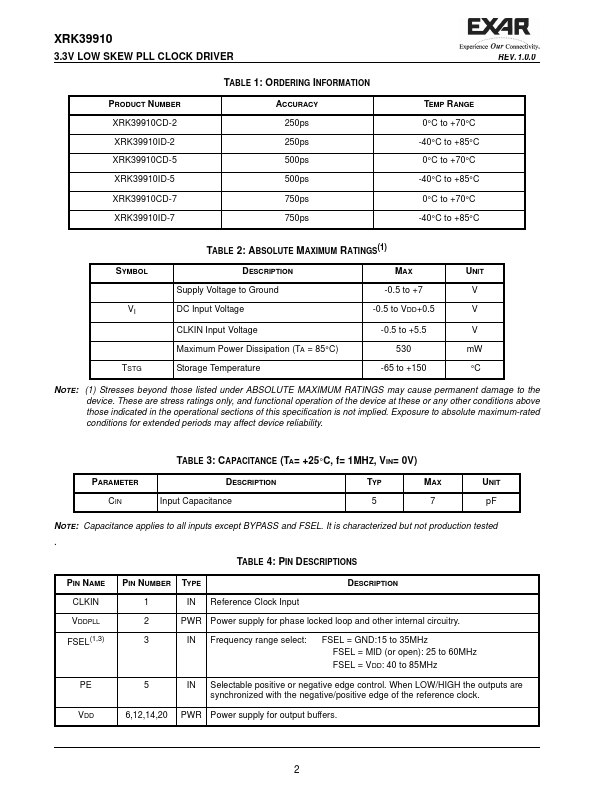

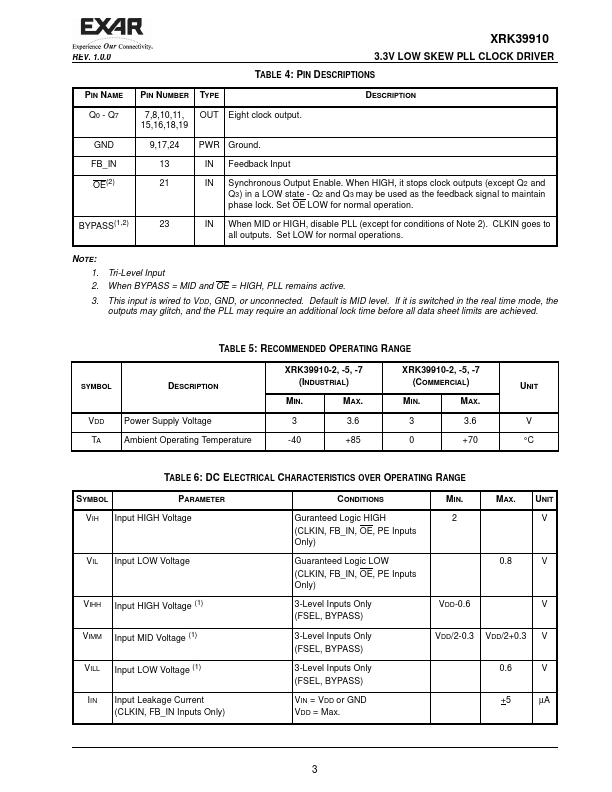

Datasheet Summary

..

JULY 2006

3.3V LOW SKEW PLL CLOCK DRIVER

REV. 1.0.0

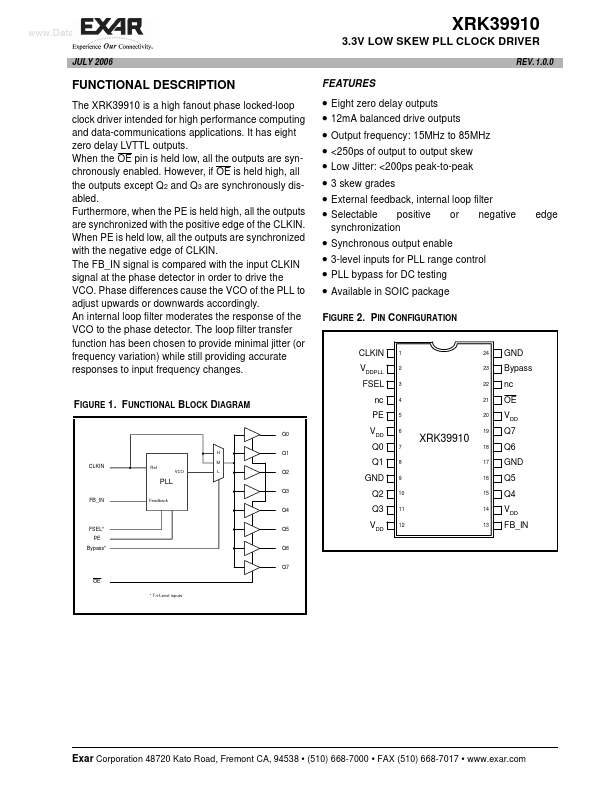

FUNCTIONAL DESCRIPTION

The XRK39910 is a high fanout phase locked-loop clock driver intended for high performance puting and data-munications applications. It has eight zero delay LVTTL outputs. When the OE pin is held low, all the outputs are synchronously enabled. However, if OE is held high, all the outputs except Q2 and Q3 are synchronously disabled. Furthermore, when the PE is held high, all the outputs are synchronized with the positive edge of the CLKIN. When PE is held low, all the outputs are synchronized with the negative edge of CLKIN. The FB_IN signal is pared with the input CLKIN signal...