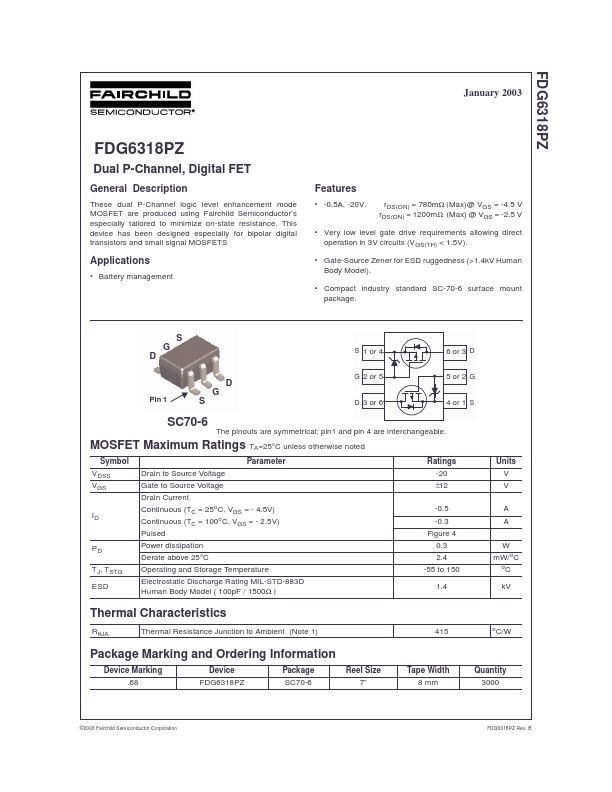

FDG6318PZ

FDG6318PZ is manufactured by Fairchild Semiconductor.

January 2003

Dual P-Channel, Digital FET

General Description

These dual P-Channel logic level enhancement mode MOSFET are produced using Fairchild Semiconductor’s especially tailored to minimize on-state resistance. This device has been designed especially for bipolar digital transistors and small signal MOSFETS

Features

- -0.5A, -20V. r DS(ON) = 780mΩ (Max)@ VGS = -4.5 V rDS(ON) = 1200mΩ (Max) @ V GS = -2.5 V

- Very low level gate drive requirements allowing direct operation in 3V circuits (V GS(TH) < 1.5V).

- Gate-Source Zener for ESD ruggedness (>1.4kV Human Body Model).

- pact industry standard SC-70-6 surface mount package.

Applications

- Battery...