FDG6301N

Overview

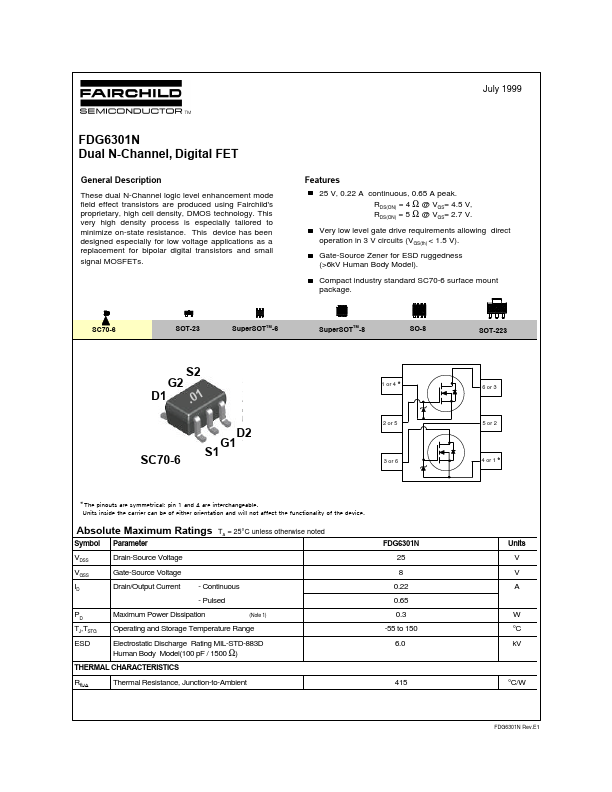

These dual N-Channel logic level enhancement mode field effect transistors are produced using Fairchild's proprietary, high cell density, DMOS technology. This very high density process is especially tailored to minimize on-state resistance.

- The pinouts are symmetrical; pin 1 and 4 are interchangeable.