Datasheet Summary

HY5DS283222BF(P)

128M(4Mx32) GDDR SDRAM

HY5DS283222BF(P)

This document is a general product description and is subject to change without notice. Hynix Semiconductor does not assume any responsibility for use of circuits described. No patent licenses are implied. Rev. 1.0 / Feb. 2005 1

1HY5DS283222BF(P)

Revision History

No. 0.1 0.2 1.0 Defined Target Spec. 1) Changed IDD & VDD_max 2) Changed tRCDWR, tWR, CL, tCK_max at 350Mhz speed bin Changed IDD Spec. Feb. 2005 History Draft Date Jun. 2004 Oct. 2004 Remark

Rev. 1.0 / Feb. 2005

1HY5DS283222BF(P)

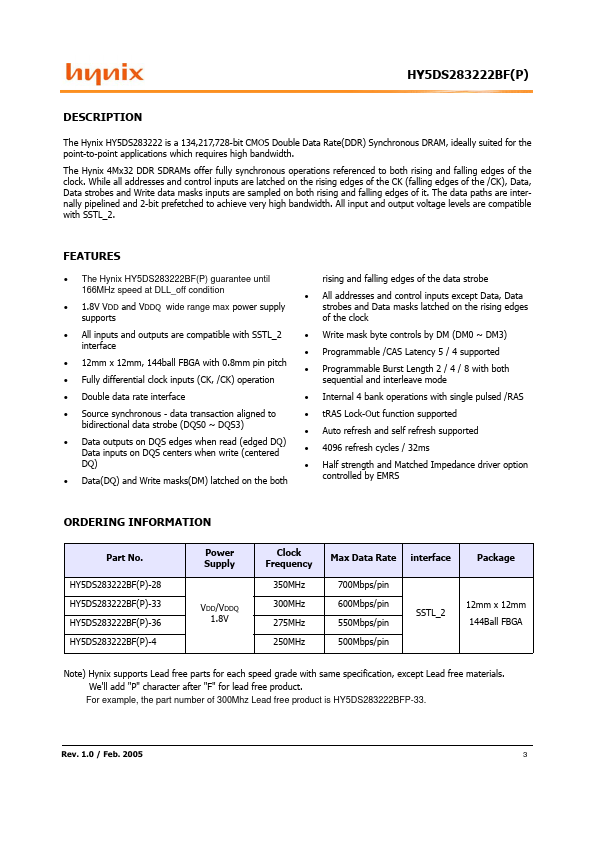

DESCRIPTION

The Hynix HY5DS283222 is a 134,217,728-bit CMOS Double Data Rate(DDR) Synchronous DRAM, ideally suited for the point-to-point...