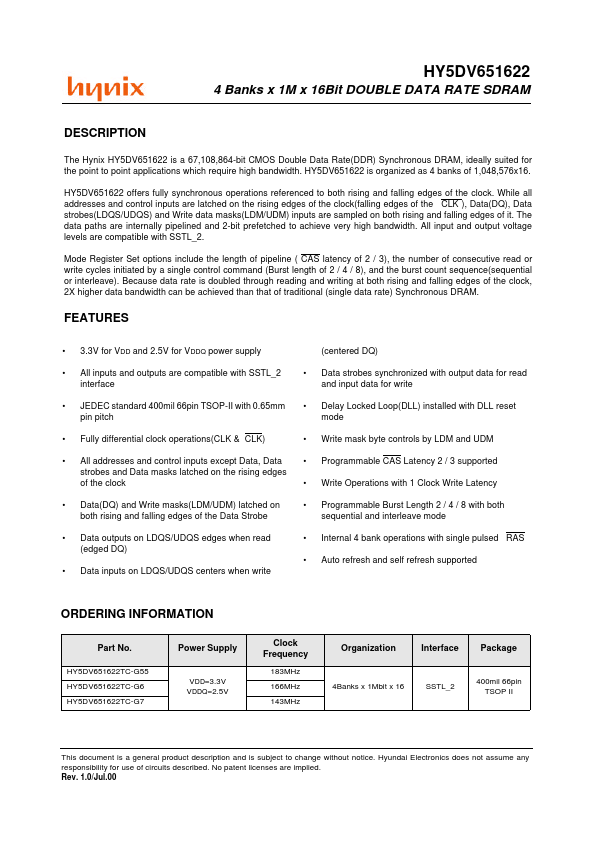

HY5DV651622

HY5DV651622 is 4 Banks x 1M x 16Bit DOUBLE DATA RATE SDRAM manufactured by SK Hynix.

4 Banks x 1M x 16Bit DOUBLE DATA RATE SDRAM

DESCRIPTION

The Hynix HY5DV651622 is a 67,108,864-bit CMOS Double Data Rate(DDR) Synchronous DRAM, ideally suited for the point to point applications which require high bandwidth. HY5DV651622 is organized as 4 banks of 1,048,576x16.

HY5DV651622 offers fully synchronous operations referenced to both rising and falling edges of the clock. While all addresses and control inputs are latched on the rising edges of the clock(falling edges of the CLK ), Data(DQ), Data strobes(LDQS/UDQS) and Write data masks(LDM/UDM) inputs are sampled on both rising and falling edges of it. The data paths are internally pipelined and 2-bit prefetched to...