9DBL06 Overview

Key Specifications

Mount Type: Surface Mount

Pins: 40

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Description

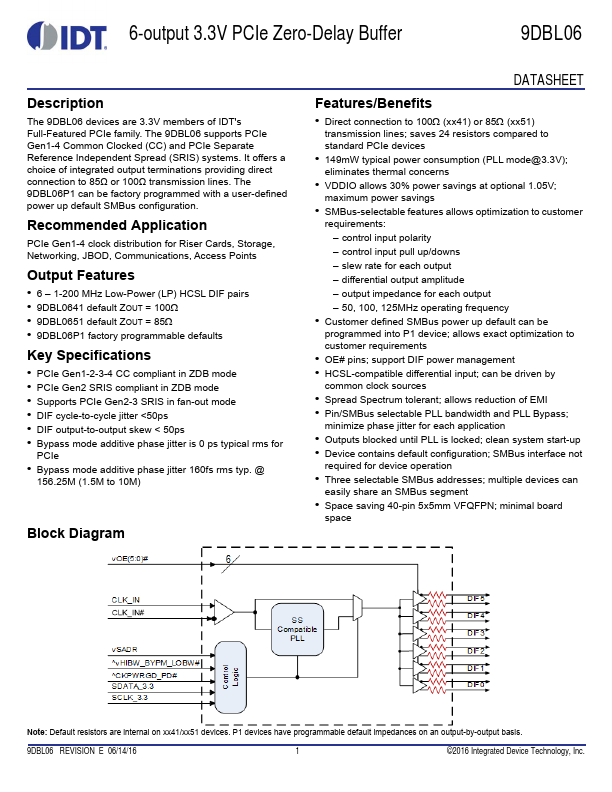

The 9DBL06 devices are 3.3V members of IDT's Full-Featured PCIe family. The 9DBL06 supports PCIe Gen1-4 Common Clocked (CC) and PCIe Separate Reference Independent Spread (SRIS) systems.

Key Features

- 6 – 1-200 MHz Low-Power (LP) HCSL DIF pairs

- 9DBL0641 default ZOUT = 100

- 9DBL0651 default ZOUT = 85

- 9DBL06P1 factory programmable defaults Key Specifications

- PCIe Gen2 SRIS compliant in ZDB mode

- Supports PCIe Gen2-3 SRIS in fan-out mode

- DIF cycle-to-cycle jitter <50ps

- DIF output-to-output skew < 50ps