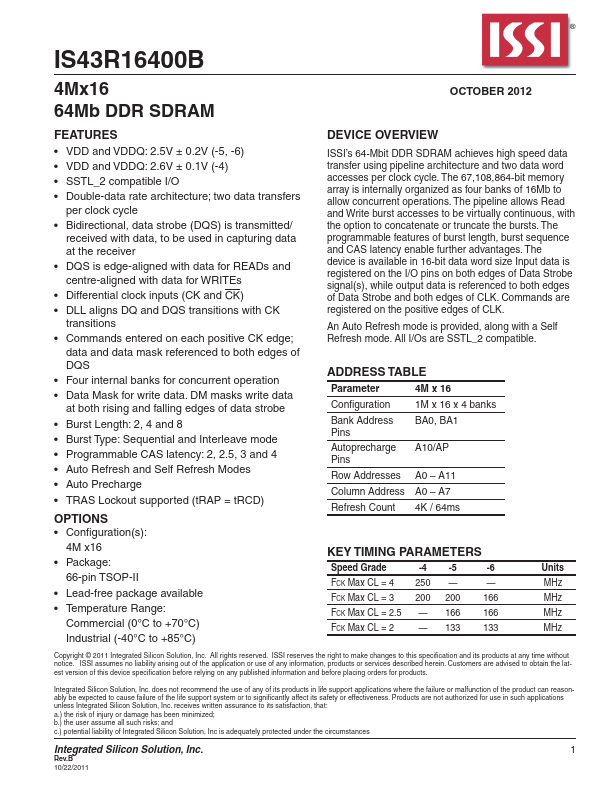

IS43R16400B

IS43R16400B is Four internal banks for concurrent operation manufactured by ISSI.

4Mx16 64Mb DDR SDRAM

Features

- -

- -

- VDD and VDDQ: 2.5V ± 0.2V (-5, -6) VDD and VDDQ: 2.6V ± 0.1V (-4) SSTL_2 patible I/O Double-data rate architecture; two data transfers per clock cycle Bidirectional, data strobe (DQS) is transmitted/ received with data, to be used in capturing data at the receiver DQS is edge-aligned with data for READs and centre-aligned with data for WRITEs Differential clock inputs (CK and CK) DLL aligns DQ and DQS transitions with CK transitions mands entered on each positive CK edge; data and data mask referenced to both edges of DQS Four internal banks for concurrent operation Data Mask for write data. DM masks write data at both rising...