IS61WV6416DBLL Overview

Key Specifications

Package: TSOP

Pins: 44

Operating Voltage: 3 V

Max Voltage (typical range): 3.6 V

Description

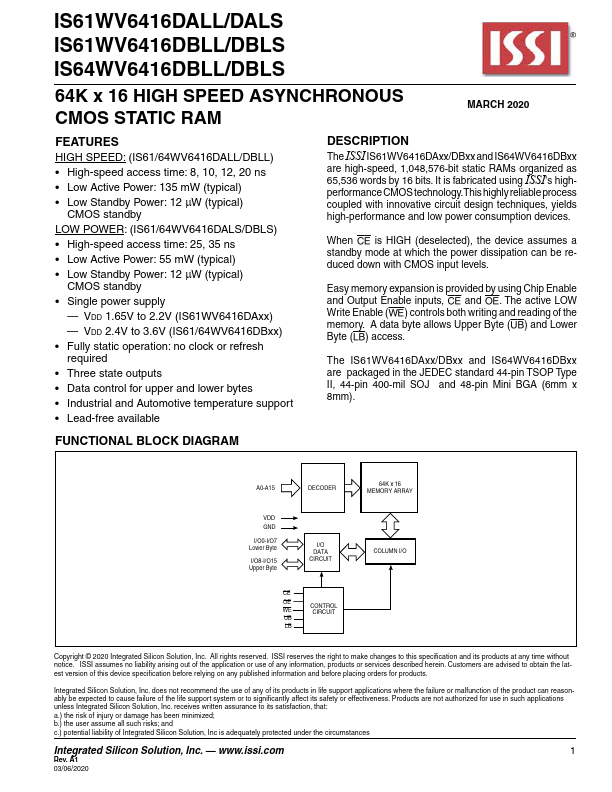

The ISSI IS61WV6416DAxx/DBxx and IS64WV6416DBxx are high-speed, 1,048,576-bit static RAMs organized as 65,536 words by 16 bits. It is fabricated using ISSI's high- performance CMOS highly reliable process coupled with innovative circuit design techniques, yields high-performance and low power consumption devices.

Key Features

- High-speed access time: 8, 10, 12, 20 ns

- Low Active Power: 135 mW (typical)

- Low Standby Power: 12 µW (typical) CMOS standby LOW POWER: (IS61/64WV6416DALS/DBLS)

- High-speed access time: 25, 35 ns

- Low Active Power: 55 mW (typical)