ICS9112CM-18

ICS9112CM-18 is Zero Delay / Low Skew Buffer manufactured by Integrated Circuit Systems.

Description w w

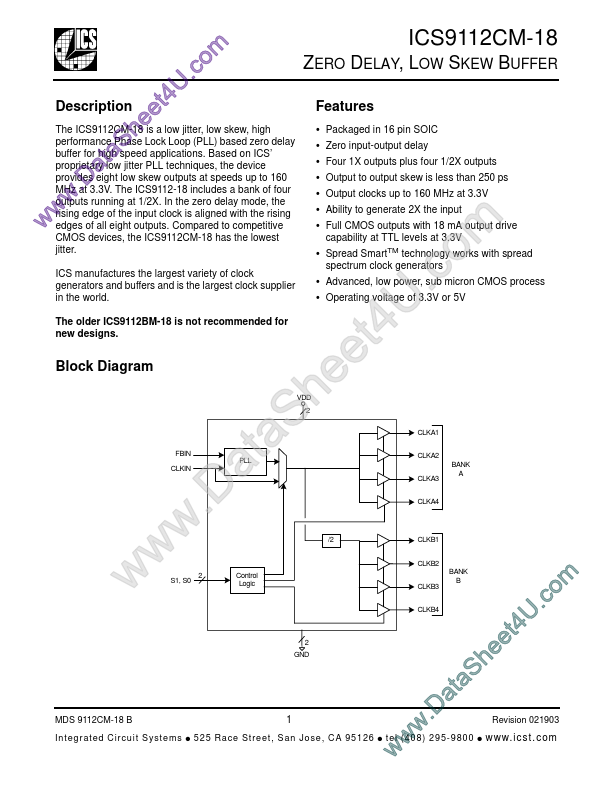

The ICS9112CM-18 is a low jitter, low skew, high performance Phase Lock Loop (PLL) based zero delay buffer for high speed applications. Based on ICS’ proprietary low jitter PLL techniques, the device provides eight low skew outputs at speeds up to 160 MHz at 3.3V. The ICS9112-18 includes a bank of four outputs running at 1/2X. In the zero delay mode, the rising edge of the input clock is aligned with the rising edges of all eight outputs. pared to petitive CMOS devices, the ICS9112CM-18 has the lowest jitter. a D . w ta

Sh ee

U 4 t

.c om

ZERO DELAY, LOW SKEW BUFFER

Features

- -

- -

- -

- Packaged in 16 pin SOIC Zero input-output delay Four 1X...