MK2049-01 Overview

Description

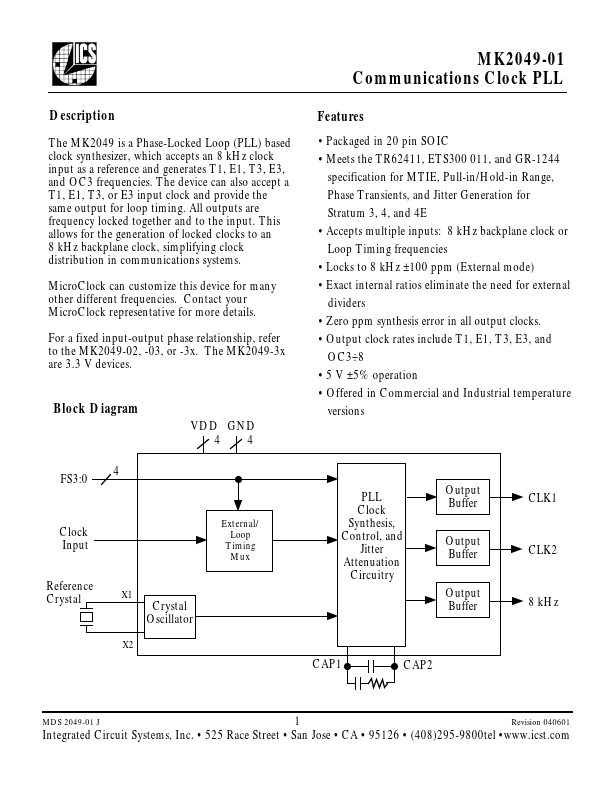

The MK2049 is a Phase-Locked Loop (PLL) based clock synthesizer, which accepts an 8 kHz clock input as a reference and generates T1, E1, T3, E3, and OC3 frequencies. The device can also accept a T1, E1, T3, or E3 input clock and provide the same output for loop timing.

Key Features

- Packaged in 20 pin SOIC

- Accepts multiple inputs: 8 kHz backplane clock or Loop Timing frequencies

- Locks to 8 kHz ±100 ppm (External mode)

- Exact internal ratios eliminate the need for external dividers

- Zero ppm synthesis error in all output clocks

- 5 V ±5% operation

- Offered in Commercial and Industrial temperature versions