MK2049-02 Overview

Description

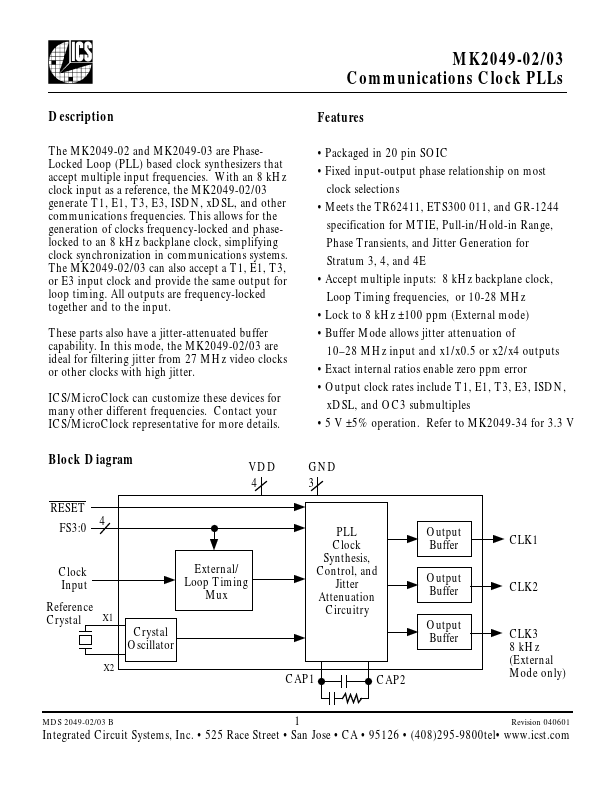

The MK2049-02 and MK2049-03 are PhaseLocked Loop (PLL) based clock synthesizers that accept multiple input frequencies. With an 8 kHz clock input as a reference, the MK2049-02/03 generate T1, E1, T3, E3, ISDN, xDSL, and other communications frequencies.

Key Features

- Packaged in 20 pin SOIC

- Fixed input-output phase relationship on most clock selections

- Accept multiple inputs: 8 kHz backplane clock, Loop Timing frequencies, or 10-28 MHz

- Lock to 8 kHz ±100 ppm (External mode)

- Buffer Mode allows jitter attenuation of 10–28 MHz input and x1/x0.5 or x2/x4 outputs

- Exact internal ratios enable zero ppm error

- Output clock rates include T1, E1, T3, E3, ISDN, xDSL, and OC3 submultiples

- 5 V ±5% operation. Refer to MK2049-34 for 3.3 V