IDT71V3556S Overview

Key Specifications

Package: LQFP

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Min Voltage (typical range): 3.135 V

Description

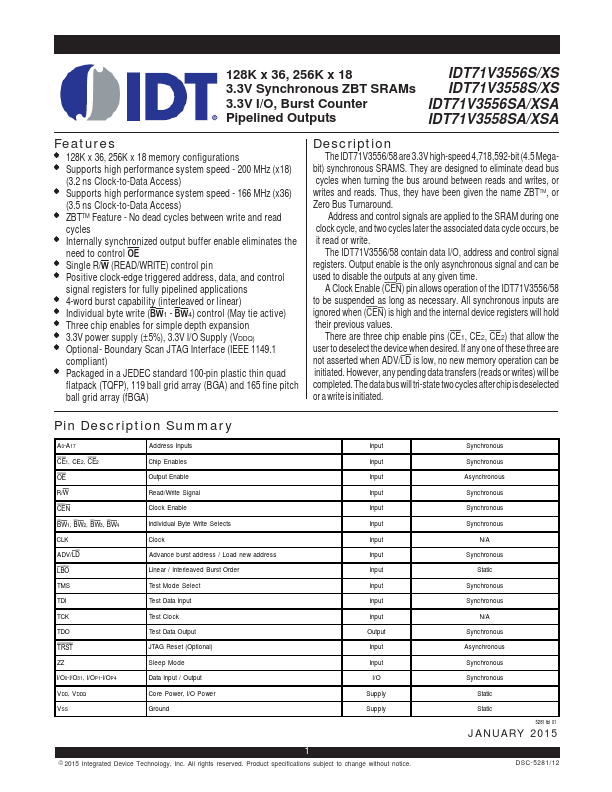

The IDT71V3556/58 are 3.3V high-speed 4,718,592-bit (4.5 Megabit) synchronous SRAMS. They are designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads.

Key Features

- 200 MHz (3.2 ns Clock-to-Data Access) ZBTTM Feature