GAL20VP8 Overview

Description

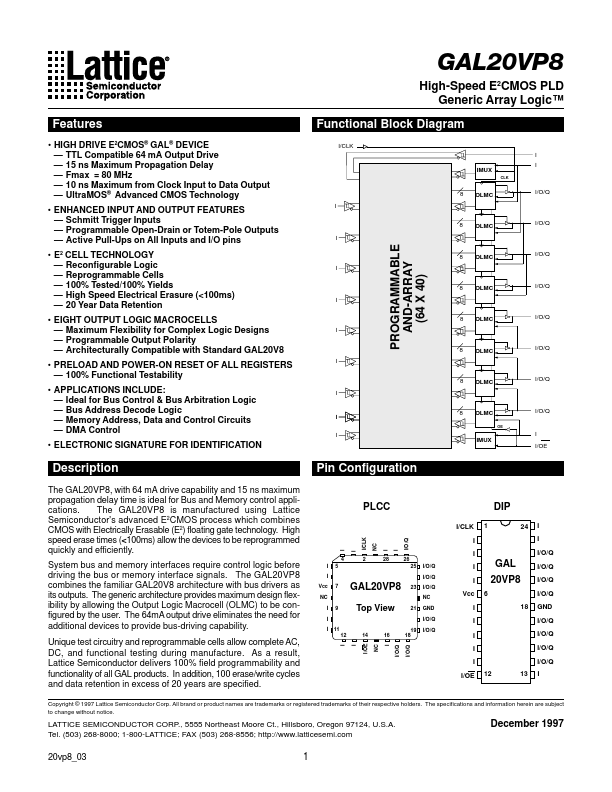

The GAL20VP8, with 64 mA drive capability and 15 ns maximum propagation delay time is ideal for Bus and Memory control applications. The GAL20VP8 is manufactured using Lattice Semiconductor's advanced E2CMOS process which combines CMOS with Electrically Erasable (E2) floating gate technology.

Key Features

- HIGH DRIVE E2CMOS® GAL® DEVICE

- TTL Compatible 64 mA Output Drive

- 15 ns Maximum Propagation Delay

- Fmax = 80 MHz

- 10 ns Maximum from Clock Input to Data Output

- UltraMOS® Advanced CMOS Technology

- ENHANCED INPUT AND OUTPUT FEATURES

- Schmitt Trigger Inputs

- Programmable Open-Drain or Totem-Pole Outputs

- Active Pull-Ups on All Inputs and I/O pins