SY89827L Overview

Key Specifications

Package: TQFP

Mount Type: Surface Mount

Pins: 64

Operating Voltage: 3.3 V

Description

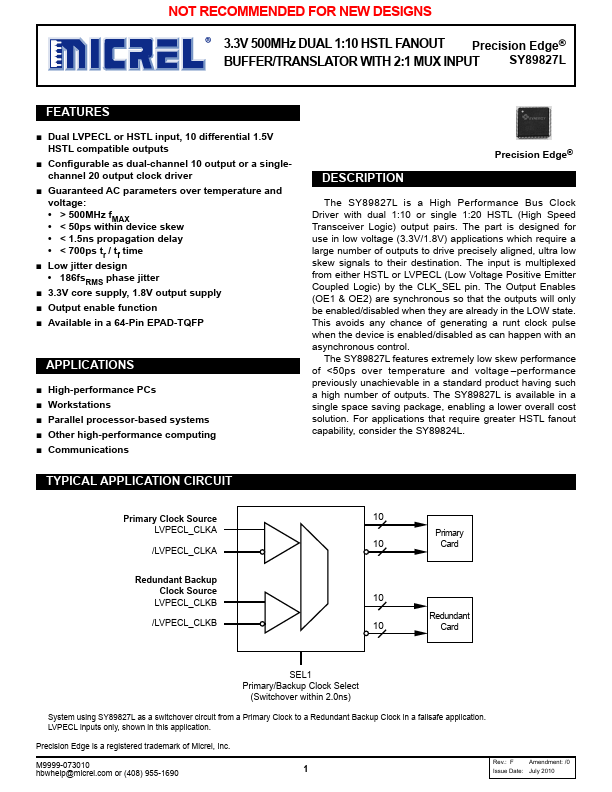

Precision Edge® The SY89827L is a High Performance Bus Clock Driver with dual 1:10 or single 1:20 HSTL (High Speed Transceiver Logic) output pairs. The part is designed for use in low voltage (3.3V/1.8V) applications which require a large number of outputs to drive precisely aligned, ultra low skew signals to their destination.

Key Features

- Dual LVPECL or HSTL input, 10 differential 1.5V HSTL compatible outputs

- Configurable as dual-channel 10 output or a singlechannel 20 output clock driver

- Guaranteed AC parameters over temperature and voltage

- > 500MHz fMAX

- < 50ps within device skew