MT48LC128M4A2

MT48LC128M4A2 is SYNCHRONOUS DRAM manufactured by Micron Technology.

- Part of the MT48LC32M16A2 comparator family.

- Part of the MT48LC32M16A2 comparator family.

FEATURES

- PC100- and PC133-pliant

- Fully synchronous; all signals registered on positive edge of system clock

- Internal pipelined operation; column address can be changed every clock cycle

- Internal banks for hiding row access/precharge

- Programmable burst lengths: 1, 2, 4, 8, or full page

- Auto Precharge, includes CONCURRENT AUTO PRECHARGE, and Auto Refresh Modes

- Self Refresh Mode

- 64ms, 8,192-cycle refresh

- LVTTL-patible inputs and outputs

- Single +3.3V ±0.3V power supply

- 32 Meg x 4 x 4 banks MT48LC64M8A2

- 16 Meg x 8 x 4 banks MT48LC32M16A2

- 8 Meg x 16 x 4 banks

For the latest data sheet, please refer to the Micron Web site: .micron./dramds

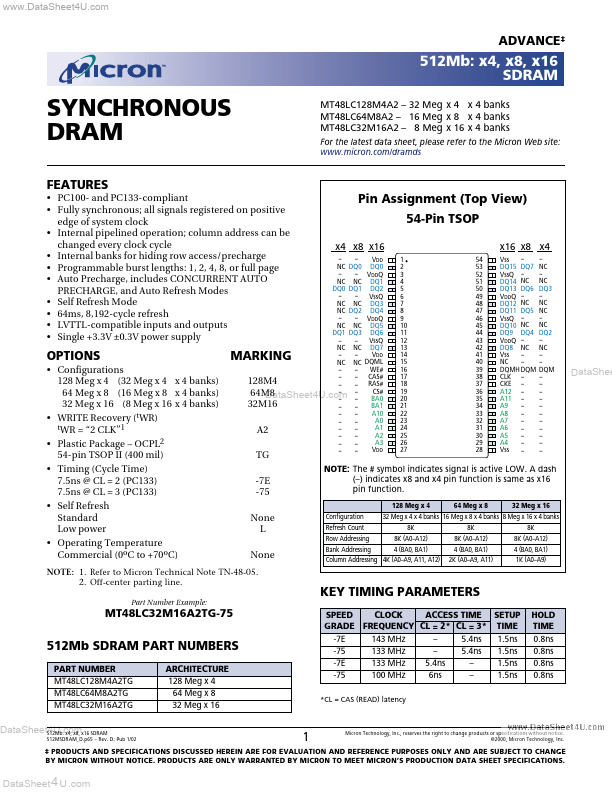

Pin Assignment (Top View) 54-Pin TSOP x4 x8 x16

NC x16 x8 x4

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28

NC DQ0 NC NC DQ0 DQ1 NC NC NC DQ2 NC NC DQ1 DQ3

OPTIONS

- Configurations 128 Meg x 4 (32 Meg x 4 x 4 banks) 64 Meg x 8 (16 Meg x 8 x 4 banks) 32 Meg x 16 (8 Meg x 16 x 4 banks)

- WRITE Recovery (t WR) t WR = “2 CLK”1

- Plastic Package

- OCPL2 54-pin TSOP II (400 mil)

- Timing (Cycle Time) 7.5ns @ CL = 2 (PC133) 7.5ns @ CL = 3 (PC133)

- Self Refresh Standard Low power

- Operating Temperature mercial (0o C to +70o C)

MARKING

128M4 64M8 . 32M16 A2 TG -7E -75 None L None

- -

- VDD DQ0 VDDQ DQ1 DQ2 Vss Q DQ3 DQ4 VDDQ DQ5 DQ6 Vss Q DQ7 VDD DQML WE# CAS# RAS# CS# BA0 BA1 A10 A0 A1 A2 A3 VDD

Vss DQ15 DQ7 Vss Q DQ14 NC DQ13 DQ6 VDDQ DQ12 NC DQ11 DQ5 Vss Q DQ10 NC DQ9 DQ4 VDDQ DQ8 NC Vss NC DQMH DQM CLK CKE A12 A11 A9 A8 A7 A6 A5 A4 Vss

- NC

NC DQ3

NC NC

NC...