MT48LC1M16A1

MT48LC1M16A1 is manufactured by Micron Technology.

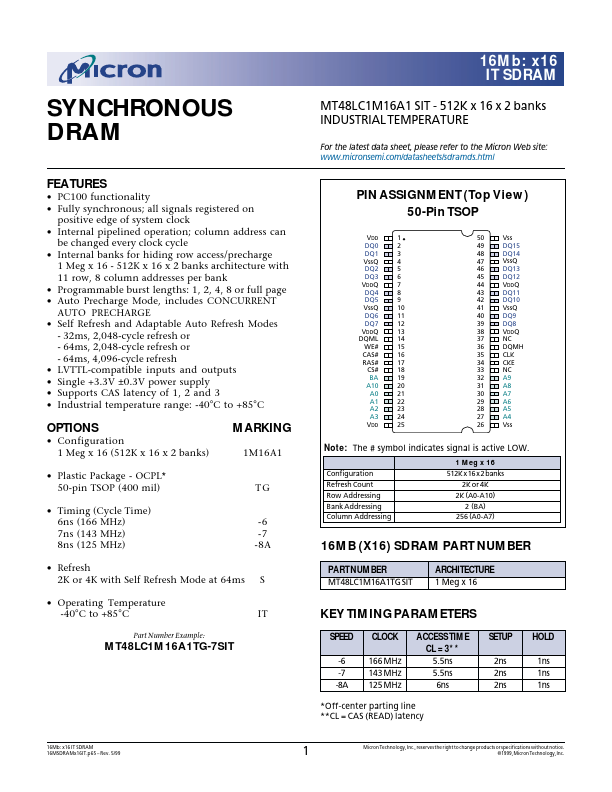

16Mb: x16 IT SDRAM

SYNCHRONOUS DRAM

Features

- PC100 functionality

- Fully synchronous; all signals registered on positive edge of system clock

- Internal pipelined operation; column address can be changed every clock cycle

- Internal banks for hiding row access/precharge 1 Meg x 16

- 512K x 16 x 2 banks architecture with 11 row, 8 column addresses per bank

- Programmable burst lengths: 1, 2, 4, 8 or full page

- Auto Precharge Mode, includes CONCURRENT AUTO PRECHARGE

- Self Refresh and Adaptable Auto Refresh Modes

- 32ms, 2,048-cycle refresh or

- 64ms, 2,048-cycle refresh or

- 64ms, 4,096-cycle refresh

- LVTTL-patible inputs and outputs

- Single +3.3V ±0.3V power supply

- Supports CAS...