ZL30166

ZL30166 is Triple Channel Network Synchronization Clock Translator manufactured by Microsemi.

Features

- Three programmable digital PLLs/Numerically Controlled Oscillators (NCOs)

- Synchronize to any clock rate from 1 KHz to 750 MHz

- Four programmable synthesizers generate any clock rate from 1 Hz to 750 MHz with low jitter for 10G PHYs

- Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC rates

- Digital PLLs filter jitter from 5.2 Hz up to 1 k Hz

- Automatic hitless reference switching and digital holdover on reference fail

- Nine input references configurable as single ended or differential and two single ended input references

- Any input reference can be fed with sync (frame pulse) or clock

- Programmable DPLLs can synchronize to sync pulse and sync pulse/clock pair

Triple Channel Network Synchronization Clock Translator

Data Sheet

Ordering Information

March 2015

ZL30166GDG2 144 Pin LBGA

Trays

Pb Free Tin/Silver/Copper

-40o C to +85o C Package Size: 13 x 13 mm

- Eight LVPECL outputs and eight LVCMOS outputs

- Operates from a single crystal resonator or clock oscillator

- Customer defined default device configuration available via OTP (One Time Programmable) memory, including input/output frequencies

- Dynamically configurable via SPI/I2C interface and volatile configuration registers

Applications

- Sync E/SONET/SDH Line Cards

- Synchronous Ethernet, 10 GBASE-R and

10 GBASE-W

- SONET/SDH, Fibre Channel, XAUI

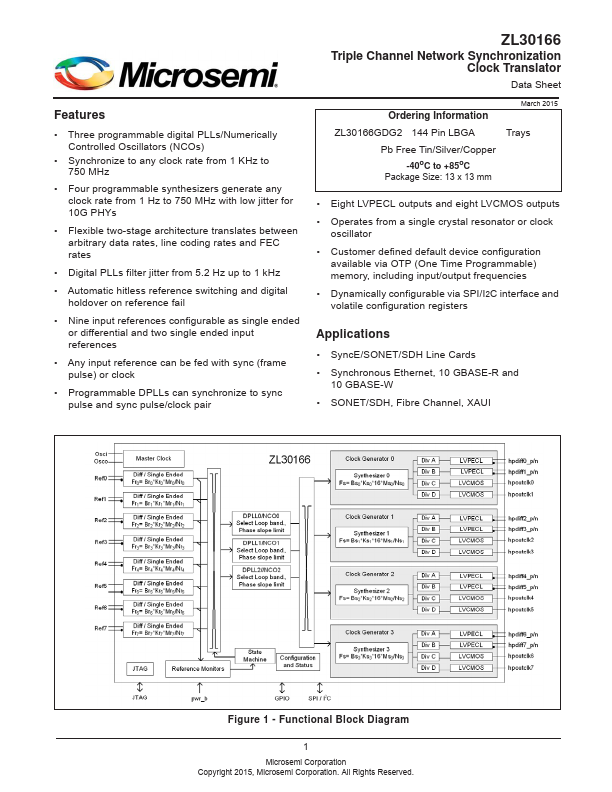

Figure 1

- Functional Block Diagram

Microsemi Corporation Copyright 2015, Microsemi Corporation. All Rights Reserved.

Data Sheet

Change History

Below are the changes from the October 2014 issue to the March 2015 issue:

Page 1

Item Added Features bullet

GPIO pin description

Figure 14 "Typical Power-Up Reset...