ZL30161 Overview

Key Specifications

Package: BGA

Pins: 144

Key Features

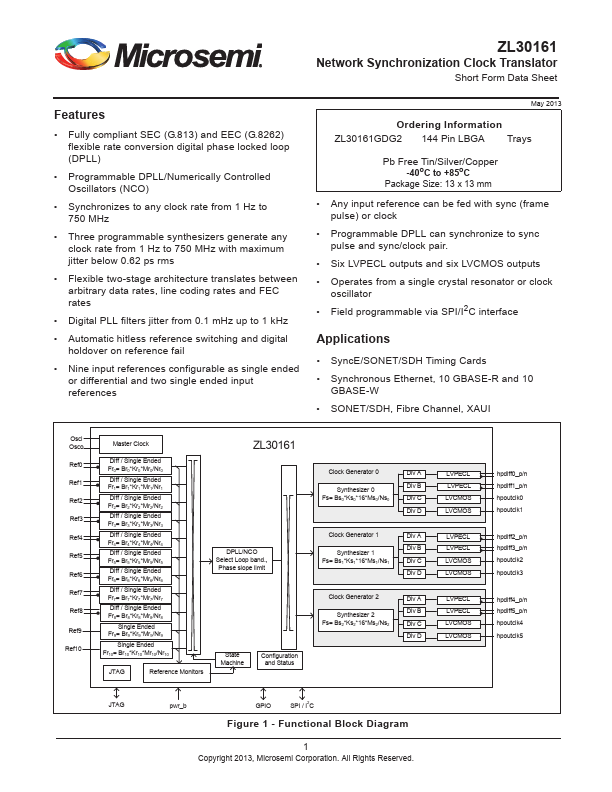

- Fully compliant SEC (G.813) and EEC (G.8262) flexible rate conversion digital phase locked loop (DPLL)

- Programmable DPLL/Numerically Controlled Oscillators (NCO)

- Synchronizes to any clock rate from 1 Hz to 750 MHz

- Three programmable synthesizers generate any clock rate from 1 Hz to 750 MHz with maximum jitter below 0.62 ps rms

- Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC rates