ZL30168

Key Features

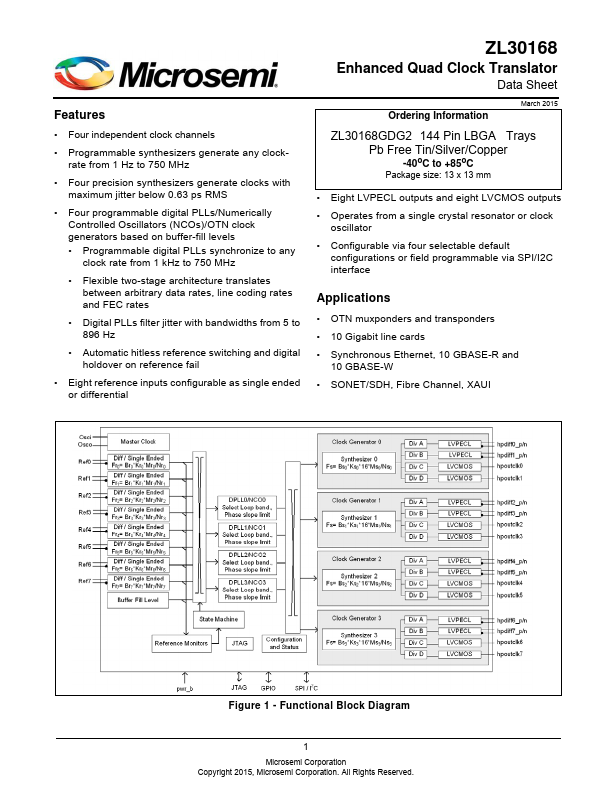

- Four independent clock channels

- Programmable synthesizers generate any clockrate from 1 Hz to 750 MHz

- Four precision synthesizers generate clocks with maximum jitter below 0.63 ps RMS

- Four programmable digital PLLs/Numerically Controlled Oscillators (NCOs)/OTN clock generators based on buffer-fill levels

- Programmable digital PLLs synchronize to any clock rate from 1 kHz to 750 MHz

Applications

- OTN muxponders and transponders