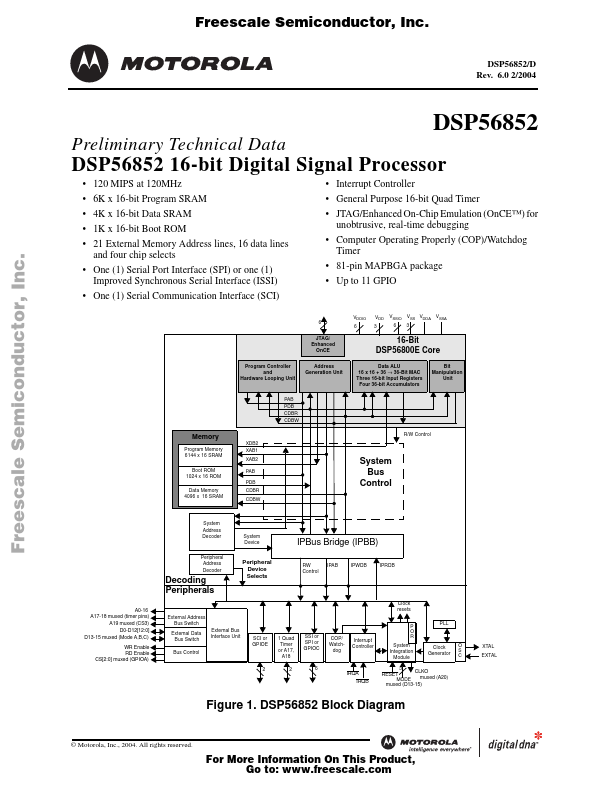

DSP56852

Key Features

- Memory Harvard architecture permits as many as three simultaneous accesses to program and data memory On-chip memory includes

- 6K × 16-bit Program SRAM

- 4K × 16-bit Data SRAM

- 1K × 16-bit Boot ROM

- 21 External Memory Address lines, 16 data lines and four (4) programmable chip select signals 1.1.3

- 81-pin MAPBGA package Up to 11 GPIO * Each peripheral I/O can be used alternately as a General Purpose I/O if not needed 1.1.4

- Energy Information Fabricated in hi