MCM63P631 Overview

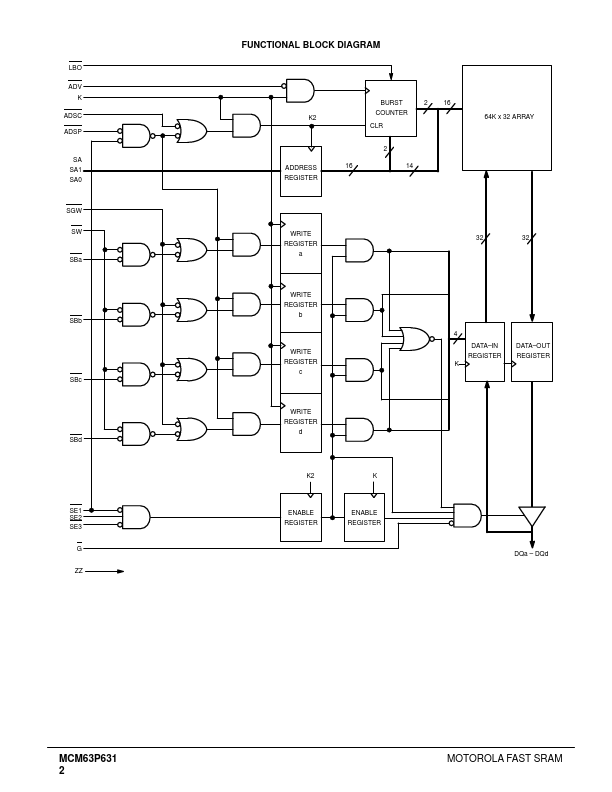

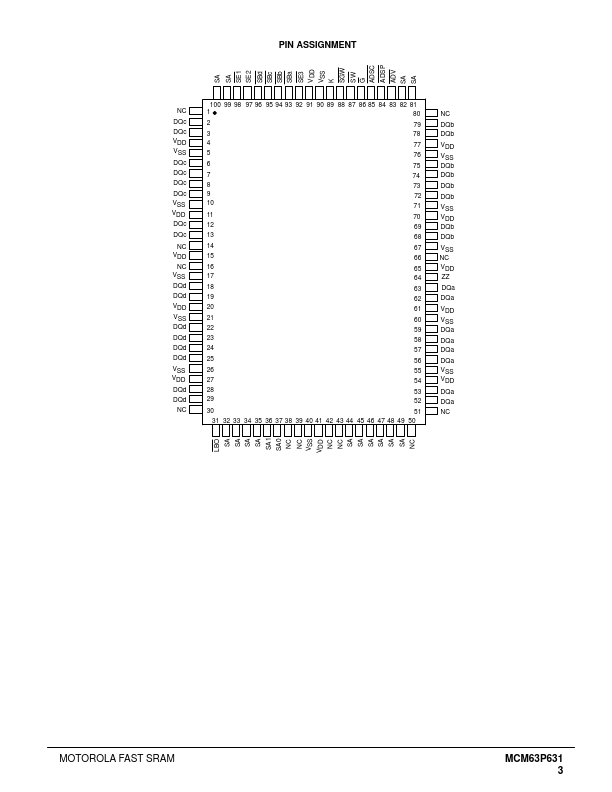

MOTOROLA SEMICONDUCTOR TECHNICAL DATA Order this document by MCM63P631/D Advance Information MCM63P631 64K x 32 Bit Pipelined BurstRAM Synchronous Fast Static RAM The MCM63P631 is a 2M bit synchronous fast static RAM designed to provide a burstable, high performance, secondary cache for the 68K Family, PowerPC™, and Pentium™ microprocessors. It is organized as 64K words of 32 bits each. This device integrates input...