DS90CF384A

Description

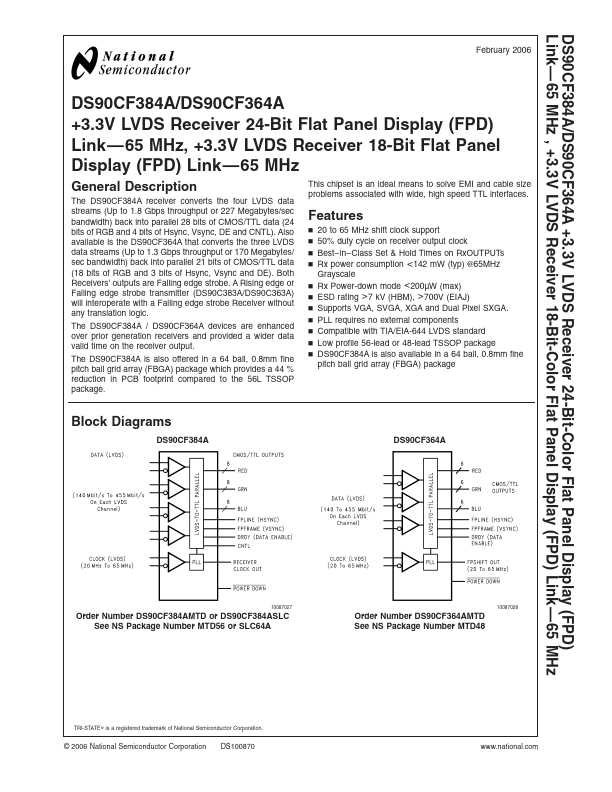

The DS90CF384A receiver converts the four LVDS data streams (Up to 1.8 Gbps throughput or 227 Megabytes/sec bandwidth) back into parallel 28 bits of CMOS/TTL data (24 bits of RGB and 4 bits of Hsync, Vsync, DE and CNTL).

Key Features

- © 2006 National Semiconductor Corporation DS100870 .national

- DS90CF384A/DS90CF364A