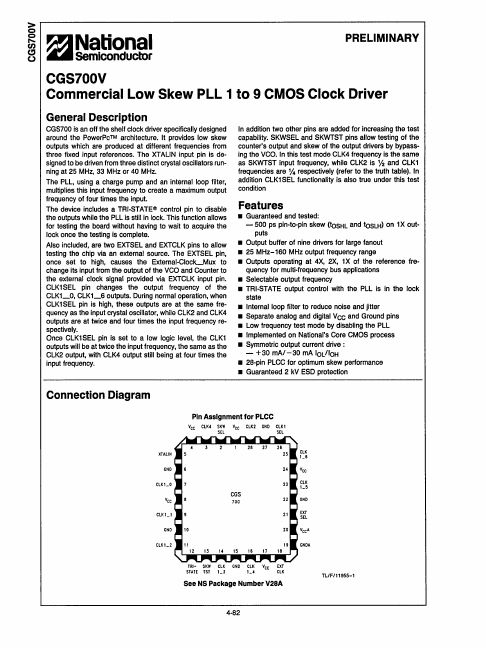

CGS700V

CGS700V is Commercial Low Skew PLL 1 to 9 CMOS Clock Driver manufactured by National Semiconductor.

Description

CGS700 is an off the shelf clock driver specifically designed around the Power Pc™ architecture. It provides low skew outputs which are produced at different frequencies from three fixed input references. The XTALIN input pin is designed to be driven from three distinct crystal oscillators running at 25 MHz, 33 MHz or 40 MHz.

The PLL, using a charge pump and an internal loop filter, multiplies this input frequency to create a maximum output frequency of four times the input.

The device includes a TRI-STATE® control pin to disable the outputs while the PLL is still in lock. This function allows for testing the board without having to wait to acquire the lock once the testing is plete.

Also included, are two EXTSEL and EXTCLK pins to allow testing the chip via an external source. The EXTSEL pin, once set to high, causes the External-Cloc LMux to change its input from the output of the VCO and Counter to the external clock signal provided via EXTCLK input pin. CLK1SEL pin changes the output frequency of the CLK1_0, CLK1_6 outputs. During normal operation, when CLK1SEL pin is high, these outputs are at the same frequency as the input crystal oscillator, while CLK2 and CLK4 outputs are at twice and four times the input frequency respectively. Once CLK1SEL pin is set to a low logic level, the CLK1 outputs will be at twice the input frequency, the same as the CLK2 output, with CLK4 output still being at four times the input frequency.

In addition two other pins are added for increasing the test capability. SKWSEL and SKWTST pins allow testing of the counter's output and skew of the output drivers by bypassing the VCO. In this test mode CLK4 frequency is the same as SKWTST input frequency, while CLK2 is V2 and CLK1 frequencies are 114 respectively (refer to the truth table). In addition CLK1 SEL functionality is also true under this test condition

Features

- Guaranteed and tested:

- 500 ps pin-to-pin skew (to SHL and to SLH) on 1X outputs

- Output buffer of nine...