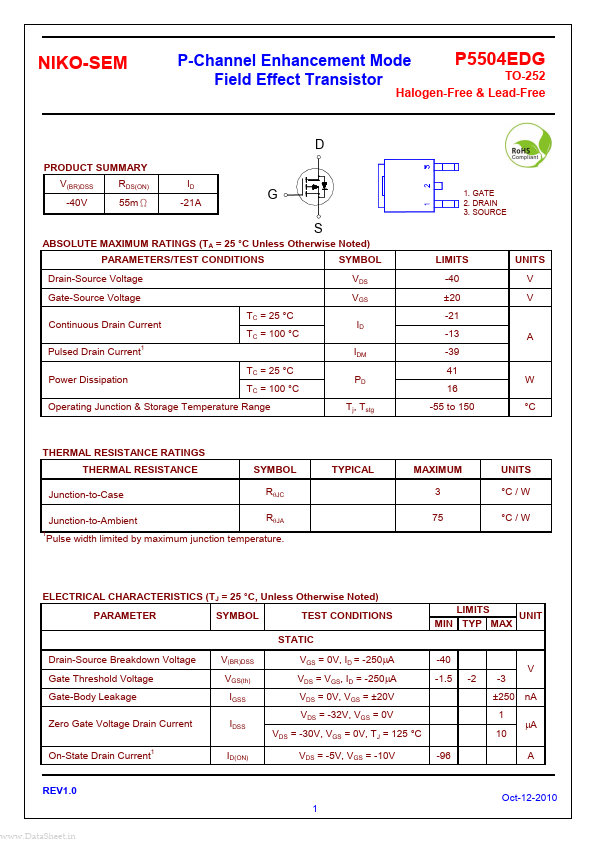

| Part | P5504EDG |

|---|---|

| Description | P-Channel Logic Level Enhancement |

| Manufacturer | Niko-Sem |

| Size | 409.47 KB |

Pricing from 0.1031 USD, available from UnikeyIC and DigiKey.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| UnikeyIC | 25000 | 2500+ : 0.1031 USD 5000+ : 0.102 USD 7500+ : 0.101 USD |

View Offer |

| DigiKey | 2421 | 1+ : 1 USD 10+ : 0.623 USD 100+ : 0.4063 USD 500+ : 0.31312 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| P5504EDG | UNIKC | P-Channel MOSFET |

| P5504EVG | UNIKC | P-Channel MOSFET |

| P5504EVG | Niko | P-Channel Logic Level Enhancement Mode Field Effect Transistor |

| P550HVN12.0 | AU Optronics | TFT LCD |

| P550HVN08.0 | AU Optronics | TFT-LCD |