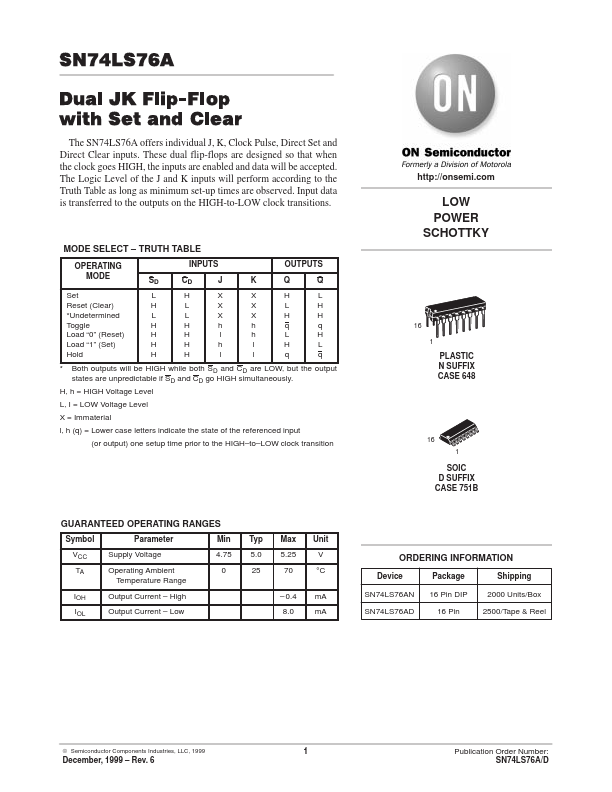

| Part | 74LS76 |

|---|---|

| Description | Dual JK Flip-Flop |

| Manufacturer | onsemi |

| Size | 93.91 KB |

Pricing from 0.1309 USD, available from UnikeyIC and Unikeyic (ICkey).Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| UnikeyIC | 10000 | 1000+ : 0.1309 USD 3000+ : 0.1288 USD |

View Offer |

| Unikeyic (ICkey) | 10000 | 1000+ : 0.1309 USD 3000+ : 0.1288 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| 74LS76A | Texas Instruments | DUAL J-K FLIP-FLOPS |

| 74LS76 | Hitachi Semiconductor | Dual J-K Flip-Flop |

| 74LS76 | Texas Instruments | DUAL J-K FLIP-FLOPS |

| 74LS76A | Motorola Semiconductor | DUAL JK FLIP-FLOP |

| 74LS76 | Unknown Manufacturer | DUAL JK FLIP-FLOP |