MC100EP196B Description

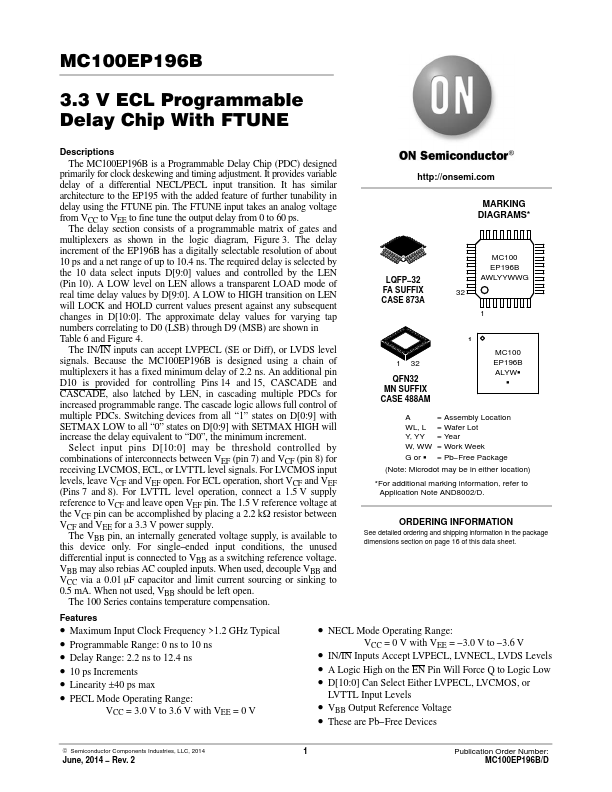

MC100EP196B 3.3 V ECL Programmable Delay Chip With FTUNE Descriptions The MC100EP196B is a Programmable Delay Chip (PDC) designed primarily for clock deskewing and timing adjustment. It provides variable delay of a differential NECL/PECL input transition. It has similar architecture to the EP195 with the added.