Datasheet Summary

2.5V/3.3V 1:5 LVPECL Fanout Buffer

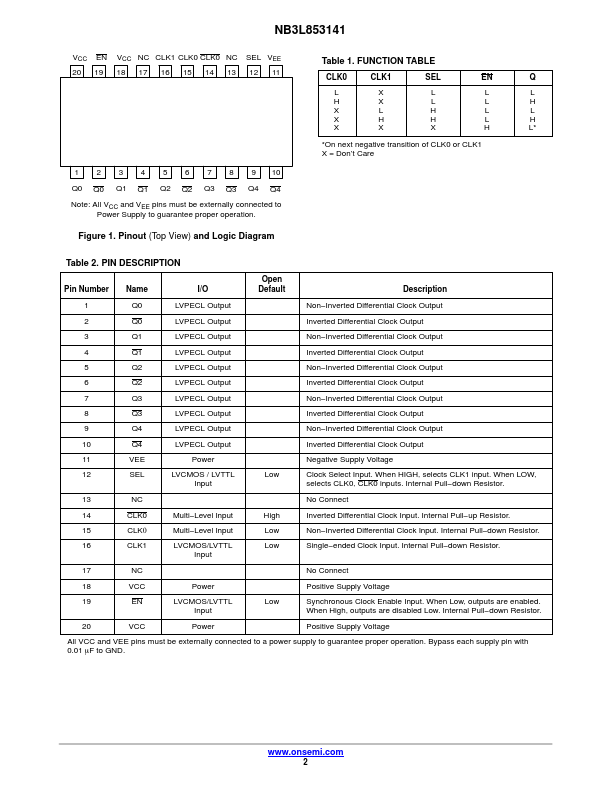

Description The NB3L853141 is a low skew 1:5 LVPECL Clock fanout buffer designed explicitly for low output skew applications. The NB3L853141 Features a multiplexed input which can be driven by either a differential or single- ended input to allow for the distribution of a lower speed clock along with the high speed system clock.

The SEL pin will select the differential clock inputs, CLK0 & CLK0, when LOW (or left open and pulled LOW by the internal pull- down resistor). When SEL is HIGH, the single- ended CLK1 input is selected.

The mon enable (EN) is synchronous so that the outputs will only be enabled/disabled when they are already in the...