PI6C2952

PI6C2952 is Low Voltage PLL Clock Driver manufactured by Pericom Semiconductor.

Features

- ±100ps Cycle-to-Cycle Jitter

- Fully Integrated PLL

- Output Frequency up to 180MHz

- High-Impedance Disabled Outputs

- patible with Power PC, Intel, and High-Performance RISC Microprocessors

- Configurable Output Frequency

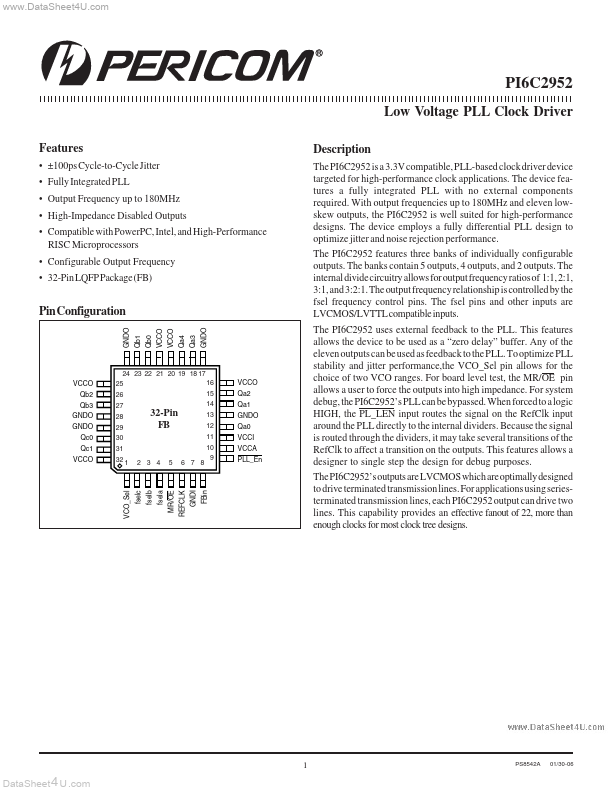

- 32-Pin LQFP Package (FB)

Description

The PI6C2952 is a 3.3V patible, PLL-based clock driver device targeted for high-performance clock applications. The device features a fully integrated PLL with no external ponents required. With output frequencies up to 180MHz and eleven lowskew outputs, the PI6C2952 is well suited for high-performance designs. The device employs a fully differential PLL design to optimize jitter and noise rejection performance. The PI6C2952 features three banks of individually configurable outputs. The banks contain 5 outputs, 4 outputs, and 2 outputs. The internal divide circuitry allows for output frequency ratios of 1:1, 2:1, 3:1, and 3:2:1. The output frequency relationship is controlled by the fsel frequency control pins. The fsel pins and other inputs are LVCMOS/LVTTL patible inputs. The PI6C2952 uses external feedback to the PLL. This features allows the device to be used as a “zero delay” buffer. Any of the eleven outputs can be used as feedback to the PLL. To optimize PLL stability and jitter performance,the VCO_Sel pin allows for the choice of two VCO ranges. For board level test, the MR/OE pin allows a user to force the outputs into high impedance. For system debug, the PI6C2952’s PLL can be bypassed. When forced to a logic HIGH, the PL_LEN input routes the signal on the Ref Clk input around the PLL directly to the internal dividers. Because the signal is routed through the dividers, it may take several transitions of the Ref Clk to affect a transition on the outputs. This features allows a designer to single step the design for debug purposes. The PI6C2952’s outputs are LVCMOS which are optimally designed to drive terminated transmission lines. For applications using seriesterminated transmission...