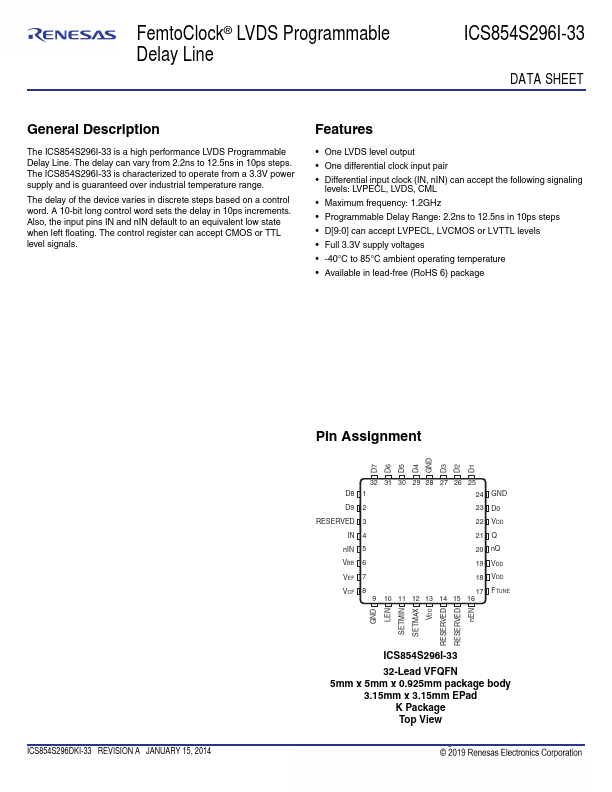

ICS854S296I-33

ICS854S296I-33 is LVDS Programmable Delay-Line manufactured by Renesas.

FemtoClock® LVDS Programmable Delay Line

DATA SHEET

General Description

The ICS854S296I-33 is a high performance LVDS Programmable Delay Line. The delay can vary from 2.2ns to 12.5ns in 10ps steps. The ICS854S296I-33 is characterized to operate from a 3.3V power supply and is guaranteed over industrial temperature range.

The delay of the device varies in discrete steps based on a control word. A 10-bit long control word sets the delay in 10ps increments. Also, the input pins IN and nIN default to an equivalent low state when left floating. The control register can accept CMOS or TTL level signals.

Features

- One LVDS level output

- One differential clock input pair

-...