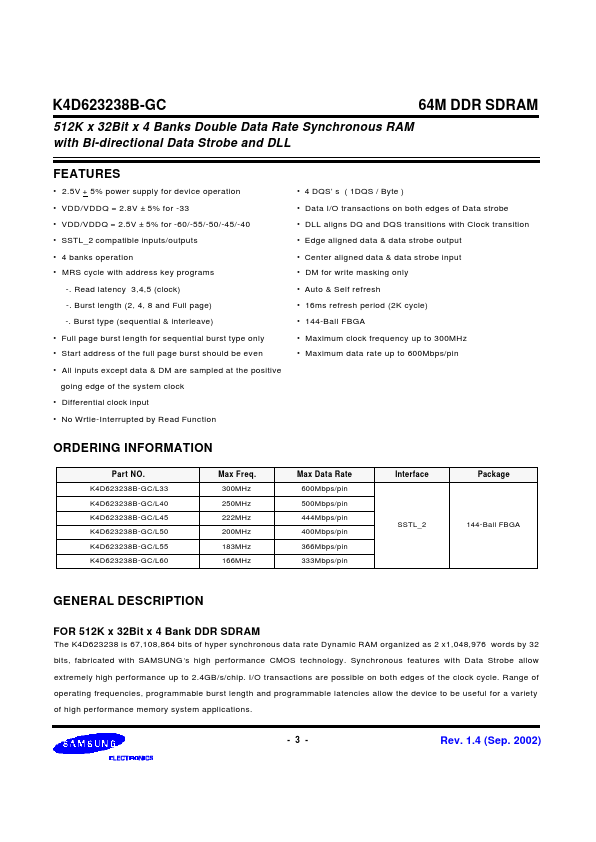

K4D623238B-GC Key Features

- 2.5V + 5% power supply for device operation

- VDD/VDDQ = 2.8V ± 5% for -33

- VDD/VDDQ = 2.5V ± 5% for -60/-55/-50/-45/-40

- SSTL_2 patible inputs/outputs

- 4 banks operation

- MRS cycle with address key programs -. Read latency 3,4,5 (clock) -. Burst length (2, 4, 8 and Full page) -. Burst type

- Full page burst length for sequential burst type only

- Start address of the full page burst should be even

- All inputs except data & DM are sampled at the positive going edge of the system clock

- Differential clock input