LH531024

LH531024 is CMOS 1M (64K x 16) MROM manufactured by Sharp Corporation.

FEATURES

- 65,536 words × 16 bit organization

- Access time: 100 ns (MAX.)

- Power consumption: Operating: 412.5 m W (MAX.) Standby: 550 µW (MAX.)

- Static operation

- TTL patible I/O

- Three-state outputs

- Single +5 V power supply

- JEDEC standard EPROM pinout (DIP)

- Packages: 40-pin, 600-mil DIP 40-pin, 525-mil SOP 44-pin, 650-mil QFJ (PLCC) DESCRIPTION

The LH531024 is a mask-programmable ROM organized as 65,536 × 16 bits. It is fabricated using silicon-gate CMOS process technology.

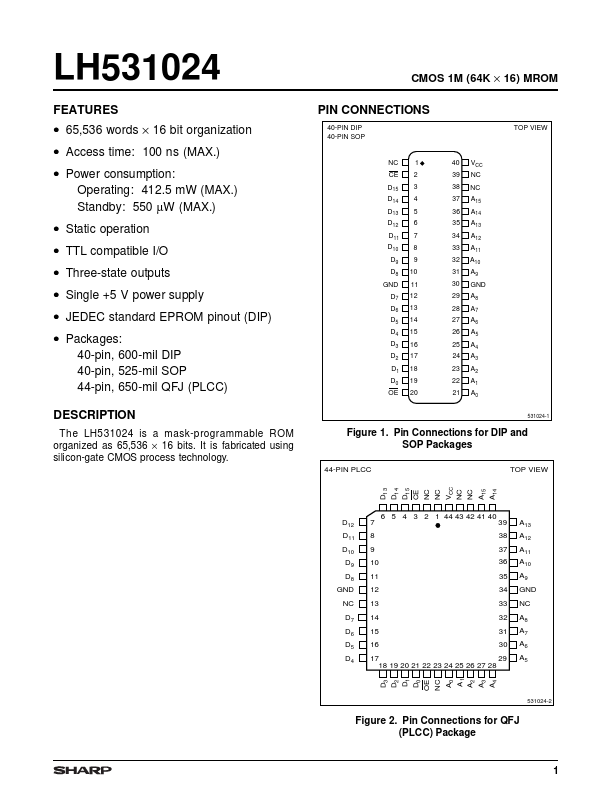

NC CE D15 D14 D13 D12 D11 D10 D9 D8 GND D7 D6 D5 D4 D3 D2 D1 D0 OE 40-PIN DIP 40-PIN SOP

CMOS 1M (64K × 16) MROM

PIN CONNECTIONS

TOP VIEW

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

VCC NC NC A15 A14 A13 A12 A11 A10 A9 GND A8 A7 A6 A5 A4 A3 A2 A1 A0

531024-1

Figure 1. Pin Connections for DIP and SOP Packages

44-PIN PLCC TOP VIEW

D12 D11 D10 D9 D8 GND NC D7 D6 D5 D4

7 8 9 10 11 12 13 14 15 16

D13 D14 D15 CE NC NC VCC NC NC A15 A14

6 5 4 3 2 1 44 43 42 41 40

39 38 37 36 35 34 33 32 31 30

A13 A12 A11 A10 A9 GND NC A8 A7 A6 A5

29 17 18 19 20 21 22 23 24 25 26 27 28

D3 D2 D1 D0 OE NC A0 A1 A2 A3 A4

531024-2

Figure 2. Pin Connections for QFJ (PLCC) Package

CMOS 1M MROM

A15 37 A14 36 A13 35 A12 34 A11 33 A10 32 A9 31 A8 29 A7 28 A6 27 A5 26 A4 25 A3 24 A2 23 A1 22 A0 21

MEMORY MATRIX (65,536 x 16) ADDRESS DECODER ADDRESS BUFFER

COLUMN SELECTOR

CE 2

CE BUFFER

TIMING GENERATOR

SENSE AMPLIFIER

OE...