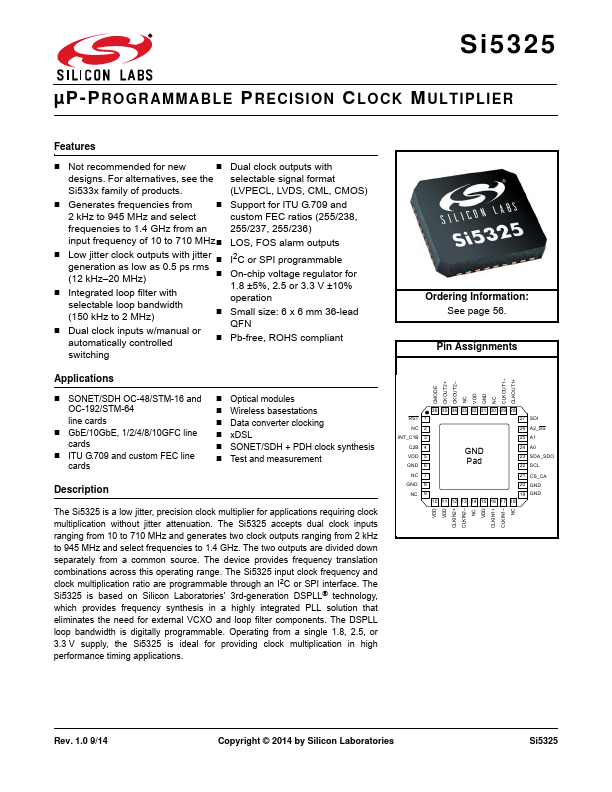

Si5325 Overview

Key Specifications

Operating Voltage: 1.8 V

Length: 6 mm

Width: 6 mm

Max Operating Temp: 85 °C

Key Features

- Not recommended for new

- Dual clock outputs with designs. For alternatives, see the selectable signal format Si533x family of products. (LVPECL, LVDS, CML, CMOS)

- Generates frequencies from

- LOS, FOS alarm outputs

- Low jitter clock outputs with jitter generation as low as 0.5 ps rms