W3E232M16S-XSTX

W3E232M16S-XSTX is 2x32Mx16bit DDR SDRAM manufactured by White Electronic.

FEATURES

Double-data-rate architecture; two data transfers per clock cycle Data rate = 200, 266, 333, 400 Mbs Package:

- 66pin TSOP II package 2.5V ±0.2V core power supply 2.5V I/O (SSTL_2 patible) Differential clock inputs(CK and CK#) DLL aligns DQ and DQS transition with CK MRS cycle with address key programs

- Read latency : 2, 2.5 , 3 (Clock)

- Burst length (2, 4, or 8)

- Burst type (sequential & interleave) Auto & Self refresh Modes

..

PRELIMINARY-

Bidirectional data strobe (DQS) transmitted/ received with data, i.e., source-synchronous data capture (one per byte) DQS edge-aligned with data for READs; centeraligned with data for WRITEs Four internal banks for concurrent operation Data mask (DM) pins for masking write data (one per byte) Programmable IOL/IOH option Auto precharge option Auto Refresh and Self Refresh Modes mercial, and Industrial Temperature Ranges Organized as 2X32M x 16

- This product is under development, is not qualified +and is subject to change without notice.

Ro HS pliant mands entered on each positive CK edge Internal pipelined double-data-rate (DDR) architecture; two data accesses per clock cycle

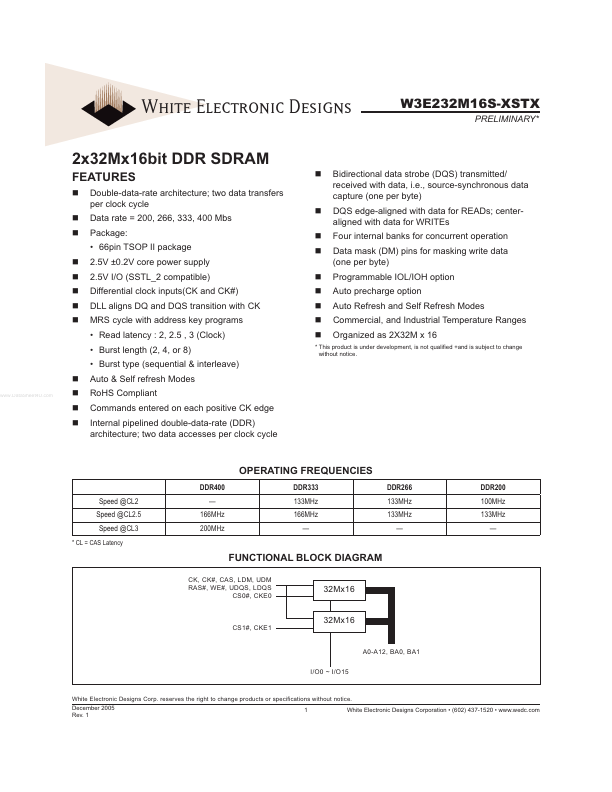

OPERATING FREQUENCIES

DDR400 Speed @CL2 Speed @CL2.5 Speed @CL3

- CL = CAS Latency

DDR333 133MHz 166MHz

- DDR266 133MHz 133MHz

- DDR200 100MHz 133MHz

- - 166MHz 200MHz

FUNCTIONAL BLOCK DIAGRAM

CK, CK#, CAS, LDM, UDM RAS#, WE#, UDQS, LDQS CS0#, CKE0

32Mx16

32Mx16

CS1#, CKE1

A0-A12, BA0, BA1 I/O0 ~ I/O15

White Electronic Designs Corp. reserves the right to change products or specifications without notice. December 2005 Rev. 1 1 White Electronic Designs Corporation

- (602) 437-1520

- .wedc.

White Electronic Designs

PIN CONFIGURATION

PRELIMINARY-

VCC DQ0 VCCQ DQ1 DQ2 VSSQ DQ3 DQ4 VCCQ DQ5 DQ6 VSSQ DQ7 NC VCCQ LDQS NC VCC DNU LDM WE# CAS# RAS# CS0# CS1# BA0 BA1 AP/A10 A0 A1 A2 A3 VCC

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33

66 65 64 63 62 61 60 59...