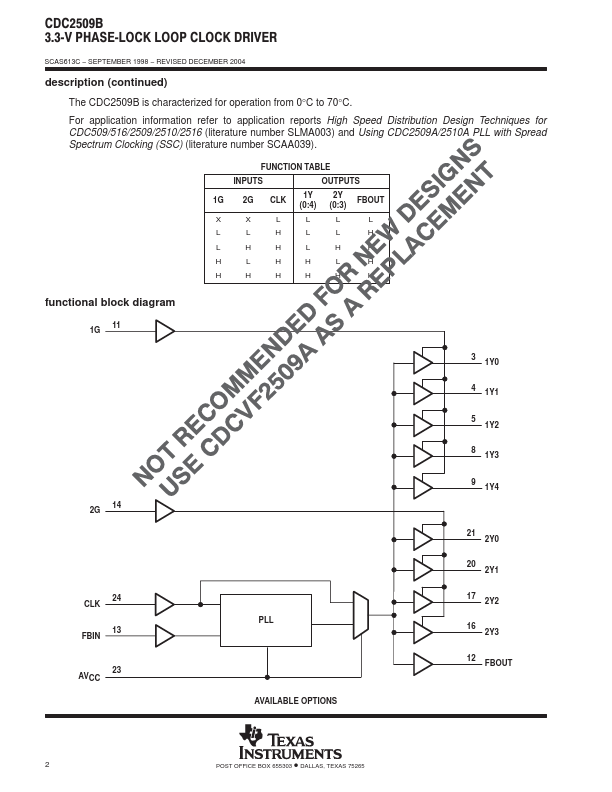

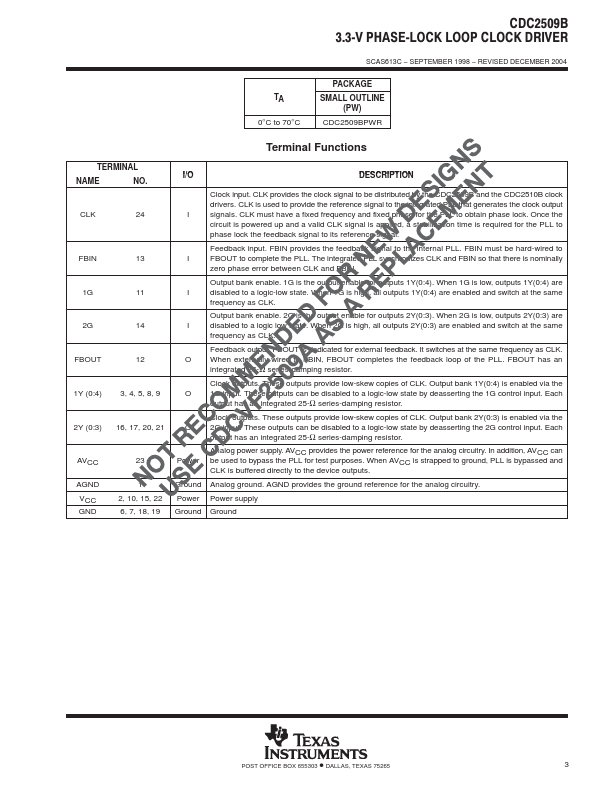

Datasheet Summary

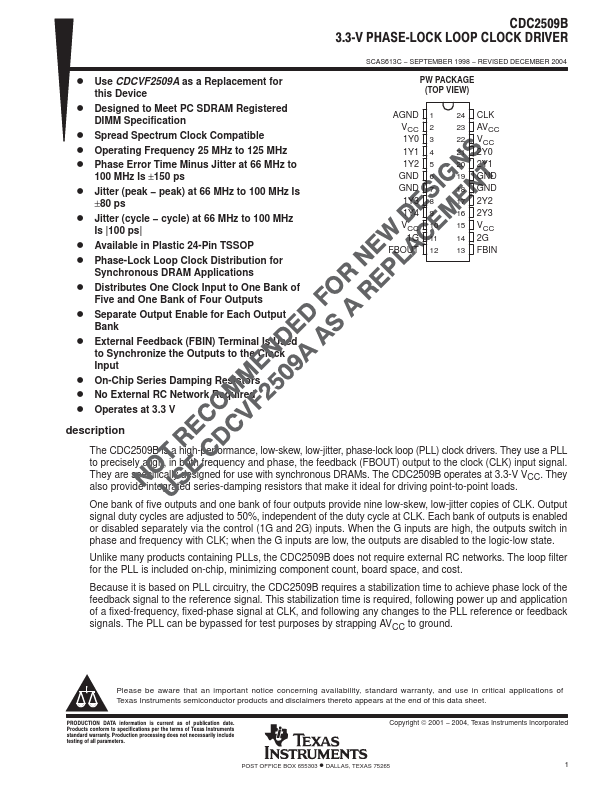

CDC2509B 3.3ĆV PHASEĆLOCK LOOP CLOCK DRIVER

ą

SCAS613C

- SEPTEMBER 1998

- REVISED DECEMBER 2004

D Use CDCVF2509A as a Replacement for this Device

D Designed to Meet PC SDRAM Registered

DIMM Specification

D Spread Spectrum Clock patible D Operating Frequency 25 MHz to 125 MHz D Phase Error Time Minus Jitter at 66 MHz to

100 MHz Is ±150 ps

D Jitter (peak

- peak) at 66 MHz to 100 MHz Is

±80 ps

D Jitter (cycle

- cycle) at 66 MHz to 100 MHz

Is |100 ps|

D Available in Plastic 24-Pin TSSOP D Phase-Lock Loop Clock Distribution for

Synchronous DRAM Applications

D Distributes One Clock Input to One Bank of

Five and One Bank of Four Outputs

D Separate Output Enable for Each Output

Bank

D External...