CDC857-3 Overview

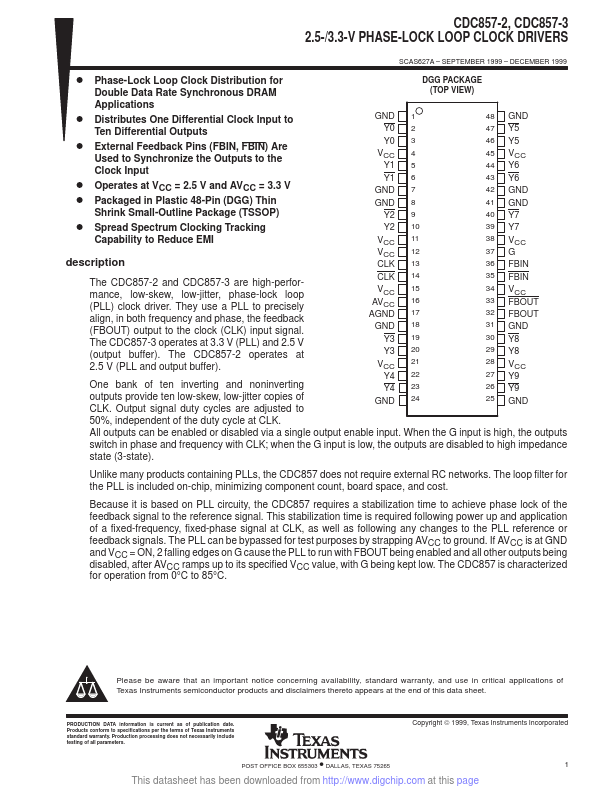

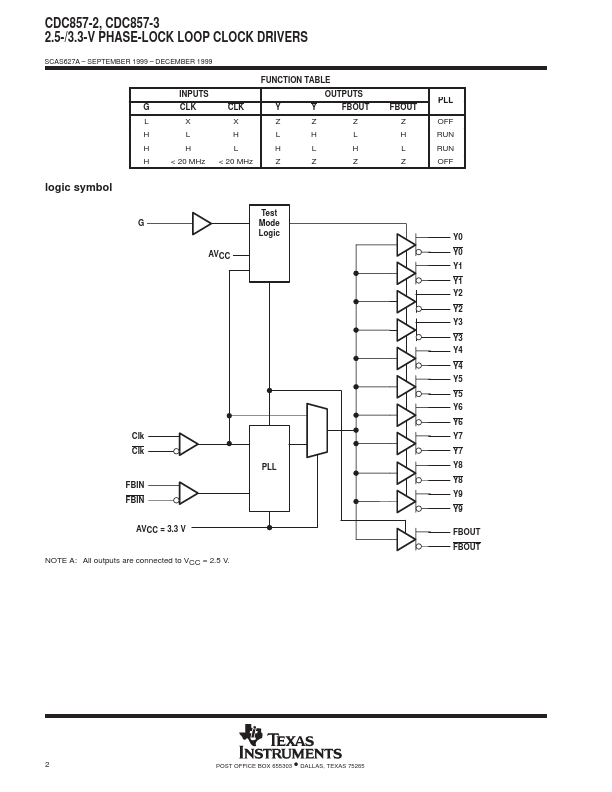

VCC 11 VCC 12 CLK 13 38 VCC 37 G 36 FBIN The CDC857-2 and CDC857-3 are high-performance, low-skew, low-jitter, phase-lock loop (PLL) clock driver. They use a PLL to precisely align, in both frequency and phase, the feedback (FBOUT) output to the clock (CLK) input signal. The CDC857-3 operates at 3.3 V (PLL) and 2.5 V (output buffer).