CDCDB2000

CDCDB2000 is manufactured by Texas Instruments.

Product Folder

Order Now

Technical Documents

Tools & Software

Support & munity

SNAS787A

- NOVEMBER 2019

- REVISED FEBRUARY 2020

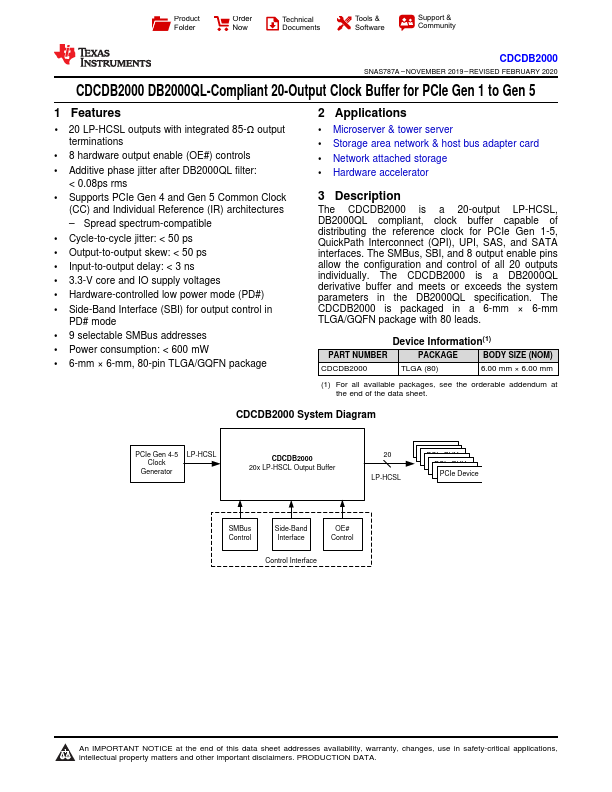

CDCDB2000 DB2000QL-pliant 20-Output Clock Buffer for PCIe Gen 1 to Gen 5

1 Features

- 1 20 LP-HCSL outputs with integrated 85-Ω output terminations

- 8 hardware output enable (OE#) controls

- Additive phase jitter after DB2000QL filter:

< 0.08ps rms

- Supports PCIe Gen 4 and Gen 5 mon Clock

(CC) and Individual Reference (IR) architectures

- Spread spectrum-patible

- Cycle-to-cycle jitter: < 50 ps

- Output-to-output skew: < 50 ps

- Input-to-output delay: < 3 ns

- 3.3-V core and IO supply voltages

- Hardware-controlled low power mode (PD#)

-...